LTC4270/LTC4271

APPLICATIONS INFORMATION

The LTC4270/LTC4271 chipset implements a proprietary

isolation scheme for inter-chip communication. This

architecture dramatically reduces BOM cost by replacing

expensiveopto-isolatorsandisolatedpowersupplieswith

a single low-cost transformer.

resistance and turns on the power. When the PD is later

disconnected, the PSE senses the open circuit and turns

power off. The PSE also turns off power in the event of a

current fault or short circuit.

When a PD is detected, the PSE optionally looks for a

classification signature that tells the PSE the maximum

power the PD will draw. The PSE can use this information

toallocatepoweramongseveralports,topolicethecurrent

consumptionofthePD,ortorejectaPDthatwilldrawmore

power than the PSE has available. The classification step

is optional; if a PSE chooses not to classify a PD, it must

assume that the PD is a 13W (full 802.3af power) device.

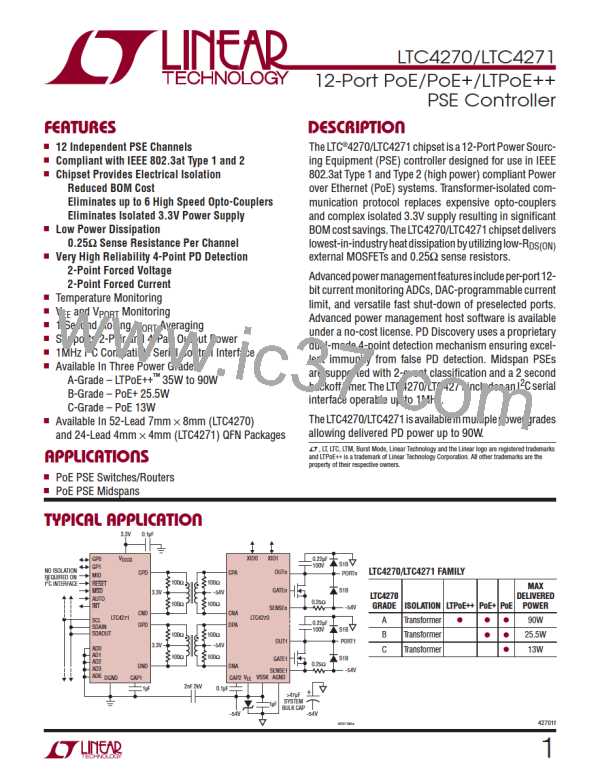

The LTC4270/LTC4271 comes in three grades which sup-

port different PD power levels.

The A-grade LTC4270/LTC4271 chipset extends PoE

++

++

power delivery capabilities to LTPoE levels. LTPoE

is a Linear Technology proprietary specification allowing

++

for the delivery of up to 90W to LTPoE compliant PDs.

++

TheLTPoE architectureextendstheIEEEphysicalpower

negotiation to include 35W, 45W, 70W and 90W power

levels. The A-grade LTC4270/LTC4271 also incorporates

all B- and C-grade features.

New in 802.3at

Thenewer802.3atstandardsupersedes802.3afandbrings

several new features:

The B-grade LTC4270/LTC4271 is a fully IEEE-compliant

Type 2 PSE supporting autonomous detection, classifica-

tion and powering of Type 1 and Type 2 PDs. The B-grade

LTC4270/LTC4271 also incorporates all C-grade features.

• A PD may draw as much as 25.5W. Such PDs (and the

PSEs that support them) are known as Type 2. Older

13W 802.3af equipment is classified as Type 1. Type 1

PDs will work with all PSEs; Type 2 PDs may require

Type 2 PSEs to work properly. The LTC4270/LTC4271

is designed to work in both Type 1 and Type 2 PSE de-

signs, and also supports non-standard configurations

at higher power levels.

The C-grade LTC4270/LTC4271 is a fully autonomous

802.3af Type 1 PSE solution. Intended for use only with

theAUTOpintiedhigh, theC-gradechipsetautonomously

supports detection, classification and powering of Type 1

PDs.AsaType1PSE,twoeventclassificationisprohibited

and Class 4 PDs are automatically treated as Class 0 PDs.

• The Classification protocol is expanded to allow Type 2

PSEs to detect Type 2 PDs, and to allow Type 2 PDs to

determine if they are connected to a Type 2 PSE. Two

versions of the new Classification protocol are avail-

able: an expanded version of the 802.3af Class Pulse

protocol, and an alternate method integrated with the

existing LLDP protocol (using the Ethernet data path).

The LTC4270/LTC4271 fully supports the new Class

Pulse protocol and is also compatible with the LLDP

protocol(whichisimplementedinthedatacommunica-

tions layer, not in the PoE circuitry).

PoE BASICS

Common Ethernet data connections consist of two or four

twisted pairs of copper wire (commonly known as CAT-5

cable), transformer-coupled at each end to avoid ground

loops. PoE systems take advantage of this coupling ar-

rangement by applying voltage between the center-taps

of the data transformers to transmit power from the PSE

to the PD without affecting data transmission. Figure 10

shows a high level PoE system schematic.

• Fault protection current levels and timing are adjusted

to reduce peak power in the MOSFET during a fault; this

allows the new 25.5W power levels to be reached using

the same MOSFETs as older 13W designs.

To avoid damaging legacy data equipment that does not

expect to see DC voltage, the PoE spec defines a protocol

that determines when the PSE may apply and remove

power. Valid PDs are required to have a specific 25k com-

mon mode resistance at their input. When such a PD is

connected to the cable, the PSE detects this signature

42701f

17

Linear [ Linear ]

Linear [ Linear ]