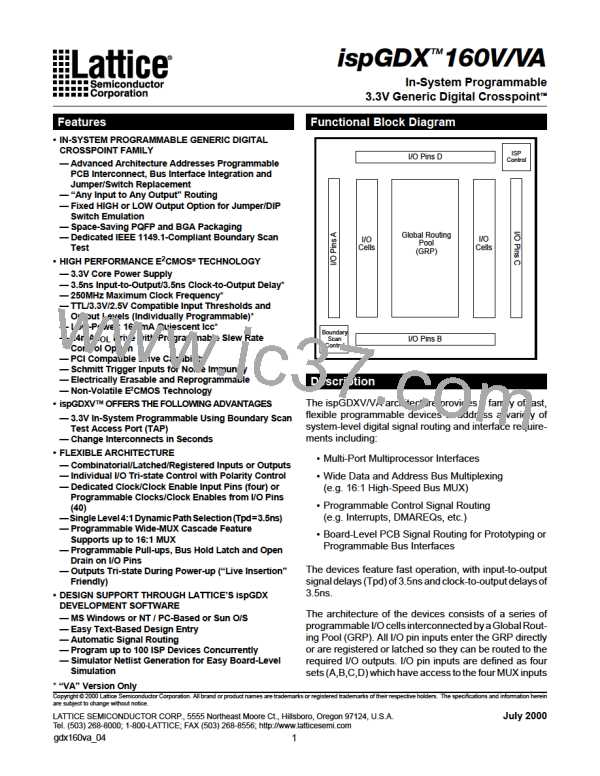

Specifications ispGDX160V/VA

In-System Programmability

All necessary programming of the ispGDXV/VA is done when the pin is left unconnected, in which case the pin is

via four TTL level logic interface signals. These four pulled high by the permanent internal pullup. This allows

signals are fed into the on-chip programming circuitry ISP programming and BSCAN testing to take place as

where a state machine controls the programming.

specified by the Instruction Table.

On-chip programming can be accomplished using an When the pin is driven low, the JTAG TAP controller is

IEEE 1149.1 boundary scan protocol. The IEEE 1149.1- driven to a reset state asynchronously. It stays there

compliant interface signals are Test Data In (TDI), Test while the pin is held low. After pulling the pin high the

Data Out (TDO), Test Clock (TCK) and Test Mode Select JTAG controller becomes active. The intent of this fea-

(TMS) control. The EPEN pin is also used to enable or tureistoallowtheJTAGinterfacetobedirectlycontrolled

disable the JTAG port.

by the data bus of an embedded controller (hence the

name Embedded Port Enable). The EPEN signal is used

as a “device select” to prevent spurious programming

and/or testing from occuring due to random bit patterns

on the data bus. Figure 9 illustrates the block diagram for

the ispJTAG interface.

The embedded controller port enable pin (EPEN) is used

to enable the JTAG tap controller and in that regard has

similar functionality to a TRST pin. When the pin is driven

high,theJTAGTAPcontrollerisenabled.Thisisalsotrue

Figure 9. ispJTAG Device Programming Interface

TDO

TDI

ispJTAG

Programming

Interface

TMS

TCK

EPEN

ispGDX

ispLSI

ispGDX

160V/VA

Device

ispGDX

160V/VA

Device

ispMACH

Device

160V/VA

Device

Device

25

LATTICE [ LATTICE SEMICONDUCTOR ]

LATTICE [ LATTICE SEMICONDUCTOR ]