Specifications ispGDX160V/VA

Signal Descriptions

Signal Name

Description

I/O

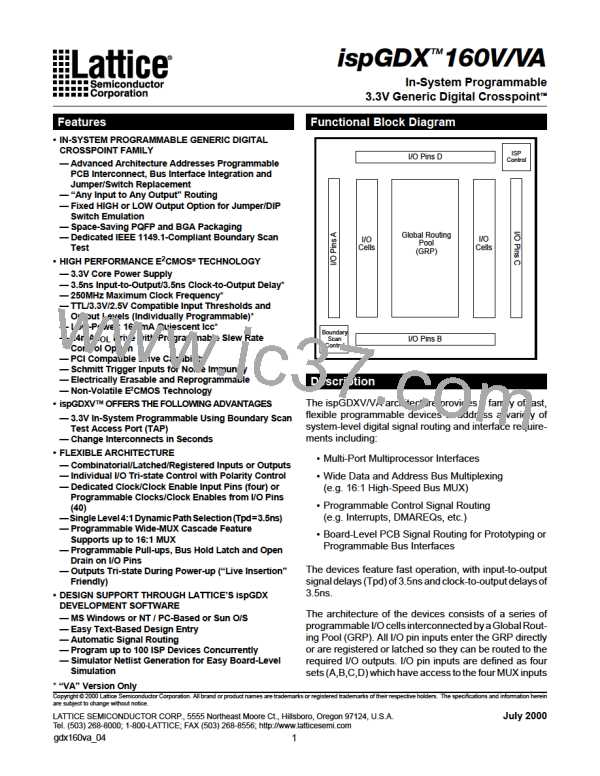

Input/Output Pins – These are the general purpose bidirectional data pins. When used as outputs,

each may be independently latched, registered or tristated. They can also each assume one other

control function (OE, CLK/CLKEN, and MUXsel as described in the text).

TOE

Test Output Enable Pin – This pin tristates all I/P pins when a logic low is driven.

Active LOW Input Pin – Resets all I/O register outputs when LOW.

Input Pins –These can be either Global Clocks or Clock Enables.

RESET

Yx/CLKENx

EPEN

Input Pin – JTAG TAP Controller Enable Pin. When high, JTAG operation is enabled. When low,

JTAG TAP controller is driven to reset.

TDI

Input Pin – Serial data input during ISP programming or Boundary Scan mode.

Input Pin – Serial data clock during ISP programming or Boundary Scan mode.

Input Pin – Control input during ISP programming or Boundary Scan mode.

Output Pin – Serial data output during ISP programming or Boundary Scan mode.

Ground (GND)

TCK

TMS

TDO

GND

VCC

VCCIO2

Vcc – Supply voltage (3.3V).

Input – This pin is used if optional 2.5V output is to be used. Every I/O can independently select either

3.3V or the optional voltage as its output level. If the optional output voltage is not required, this pin

must be connected to the VCC supply. Programmable pull-up resistors and bus-hold latches only draw

current from this supply.

NC1

No Connect.

1. NC pins are not to be connected to any active signals, VCC or GND.

2. “VA” version only.

29

LATTICE [ LATTICE SEMICONDUCTOR ]

LATTICE [ LATTICE SEMICONDUCTOR ]