®

IS42S32200

ISSI

WRITE with Auto Precharge

one clock prior to the READ to bank m.

4.InterruptedbyaWRITE(withorwithoutautoprecharge):

WRITE to bank m will interrupt a WRITE on bank n when

3. Interrupted by a READ (with or without auto precharge):

AREADtobankmwillinterruptaWRITEonbanknwhen

registered, with the data-out appearing CAS latency later.

The PRECHARGE to bank n will begin after tWR is met,

wheretWR beginswhentheREADtobankmisregistered.

The last valid WRITE to bank n will be data-in registered

A

registered. The PRECHARGE to bank n will begin after

tWR is met, where tWR begins when the WRITE to bank

m is registered. The last valid data WRITE to bank n will

be data registered one clock prior to a WRITE to bank m.

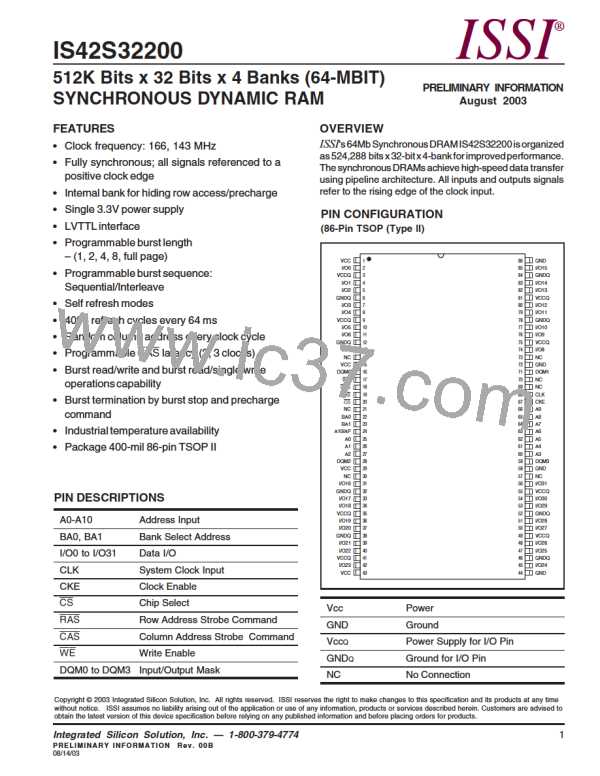

Fig CAP 3 - WRITE With Auto Precharge interrupted by a READ

T0

T1

T2

T3

T4

T5

T6

T7

CLK

COMMAND

BANK n

WRITE - AP

BANK n

READ - AP

BANK m

NOP

NOP

NOP

NOP

NOP

NOP

Page Active

WRITE with Burst of 4 Interrupt Burst, Write-Back

WR - BANK n

Precharge

t

tRP - BANK n

Internal States

tRP - BANK m

BANK m

Page Active

READ with Burst of 4

Precharge

BANK n,

COL a

BANK m,

COL b

ADDRESS

DQ

D

IN

a

DIN a+1

DOUT

b

DOUT b+1

CAS Latency - 3 (BANK m)

DON'T CARE

Fig CAP 4 - WRITE With Auto Precharge interrupted by a WRITE

T0

T1

T2

T3

T4

T5

T6

T7

CLK

COMMAND

BANK n

WRITE - AP

BANK n

WRITE - AP

BANK m

NOP

NOP

NOP

NOP

NOP

NOP

Page Active

WRITE with Burst of 4

Interrupt Burst, Write-Back

WR - BANK n

Precharge

t

t

RP - BANK n

Internal States

tRP - BANK m

BANK m

Page Active

WRITE with Burst of 4

Write-Back

BANK n,

COL a

BANK m,

COL b

ADDRESS

DQ

D

IN

a

DIN a+1

DIN a+2

D

IN

b

DIN b+1

DIN b+2

DIN b+3

DON'T CARE

30

Integrated Silicon Solution, Inc. — 1-800-379-4774

ADVANCE INFORMATION Rev. 00B

08/14/03

ISSI [ INTEGRATED SILICON SOLUTION, INC ]

ISSI [ INTEGRATED SILICON SOLUTION, INC ]