®

IS42S32200

ISSI

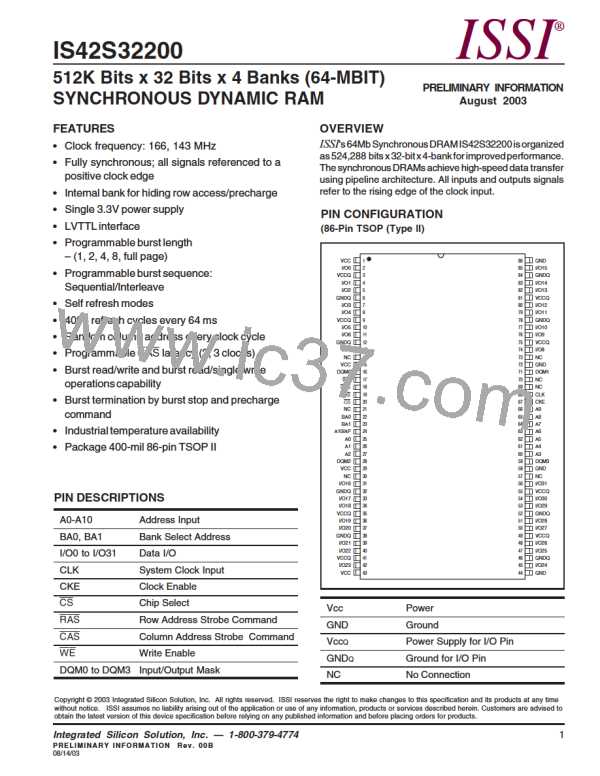

PRECHARGECommand

PRECHARGE

The PRECHARGE command (see figure) is used to

deactivate the open row in a particular bank or the open

row in all banks. The bank(s) will be available for a

subsequent row access some specified time (tRP) after

the PRECHARGE command is issued. Input A10 deter-

mines whether one or all banks are to be precharged, and

in the case where only one bank is to be precharged,

inputs BA0, BA1 select the bank. When all banks are to be

precharged, inputs BA0, BA1 are treated as “Don’t Care.”

Onceabankhasbeenprecharged,itisintheidlestateand

must be activated prior to any READ or WRITE com-

mands being issued to that bank.

CLK

HIGH - Z

CKE

CS

RAS

CAS

WE

A0-A9

ALL BANKS

A10

POWER-DOWN

BANK SELECT

Power-down occurs if CKE is registered LOW coincident

with a NOP or COMMAND INHIBIT when no accesses are

in progress. If power-down occurs when all banks are idle,

this mode is referred to as precharge power-down; if

power-down occurs when there is a row active in either

bank, this mode is referred to as active power-down.

Entering power-down deactivates the input and output

buffers, excluding CKE, for maximum power savings

while in standby. The device may not remain in the power-

down state longer than the refresh period (64ms) since no

refresh operations are performed in this mode.

BANK ADDRESS

BA0, BA1

The power-down state is exited by registering a NOP or

COMMAND INHIBIT and CKE HIGH at the desired clock

edge (meeting tCKS). See figure below.

POWER-DOWN

CLK

tCKS

≥ tCKS

CKE

COMMAND

NOP

NOP

ACTIVE

t

t

t

RCD

RAS

RC

All banks idle

Input buffers gated off

Enter power-down mode

Exit power-down mode

DON'T CARE

Integrated Silicon Solution, Inc. — 1-800-379-4774

27

ADVANCE INFORMATION Rev. 00B

08/14/03

ISSI [ INTEGRATED SILICON SOLUTION, INC ]

ISSI [ INTEGRATED SILICON SOLUTION, INC ]