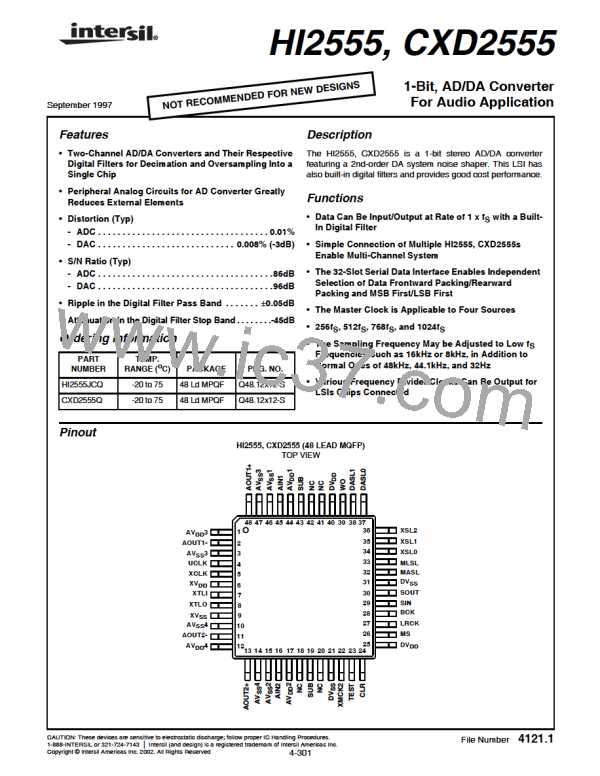

HI2555, CXD2555

Master Mode/Slave Mode

Crystal Oscillator Frequency Selection

(f = 32kHz to 48kHz)

S

(Related Pins) MS, LRCK, BCK

(Related Pins) XTLI, XTLO, XSLO, XSL1, XSL2, UNCLK,

XCLK

When using the XCS2555Q in multiple units or in a pair with

DA converters such as the CXD2558M, one of these

CXD2555Qs should be in the master mode to serve as the

source of clocks LRCK and BCK. The other CXD2555Qs are

used in the slave mode, with their clocks LRCK and BCK

supplied by the master CXD2555Q.

By setting a combination of XSLO and XSL1, with XSL2

fixed Low, the frequency of the external crystal oscillator

connected to XTLI and XTLO can be selected. In this case,

XCLK outputs a clock whose frequency is always 256 times

f , and UCLK outputs a clock that is half the crystal oscillator

S

TABLE 3.

frequency.

MS

H

MODE

LRCK AND BCK I/O

When supplying the master clock fro some other external

source, not a crystal oscillator, use XTLI for this clock input

and leave XTLO open.

Master Mode

Slave Mode

Output

Input

L

TABLE 4.

CRYSTAL OSCILLATOR FREQUENCY

256f

XSL2

XSL1

XSL0

XCLK

256f

UCLK

128f

L

L

L

L

L

L

L

H

L

S

S

S

512f

256f

256f

S

S

S

H

H

768f

256f

384f

S

S

S

H

1024f

256f

512f

S

S

S

INPUT

INPUT

OUTPUT

OUTPUT

LRCK

LRCK

CXD2555Q

(SLAVE MODE)

MS

L

H

MS

(MASTER MODE)

BCK

CXD2555Q

BCK

INPUT

INPUT

LRCK

BCK

CXD2558M

FIGURE 37. CONNECTION EXAMPLE

Crystal Oscillator Frequency Selection

(f = 8kHz to 24kHz)

S

512f

256f

S

S

TO EXTERNAL IC,

SUCH AS DSP

UCLK

CXD2555Q

L

XSL2

XSL1

XSL0

(Related Pins) XTLI, XTLO, XSLO, XSL1, XSL2, UNCLK,

XCLK

H

H

TO CXD2555Q IN

SLAVE MODE

With XSL2 fixed High, the device can be operated with low-

XCLK

XTL0

f

frequencies which may be 1/2 or 1/4 the normal f

S

S

XTL1

frequency. In this case, the frequency of the crystal oscillator

can be selected by setting a combination of XSL0 and XSL1

accordingly.

1024f

S

FIGURE 38. CONNECTION EXAMPLE

Example: When input level = 1.4V (4V

AD Converter Input Level

)

P-P

RMS

Given the constants shown in the Test Circuit on page 7, the

R

= 4200 • 1.4 - 1200 = 4680

AD converter input level V (operational amplifier input IN)

IN

IN

→ 4700 [Ω]

is such that 4V

(1.4V

) is equivalent to the full-scale

RMS

P-P

output. Also, the large-amplitude inputs are possible by

varying the AD converter input resistance value (R ). Use

IN

the equation shown below to calculate this resistance value.

The AD converter generates full-scale outputs for inputs

equal to or greater than the values thus obtained.

R

= 420 • V [RMS] - 1200 [Ω]

IN

IN

4-308

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]