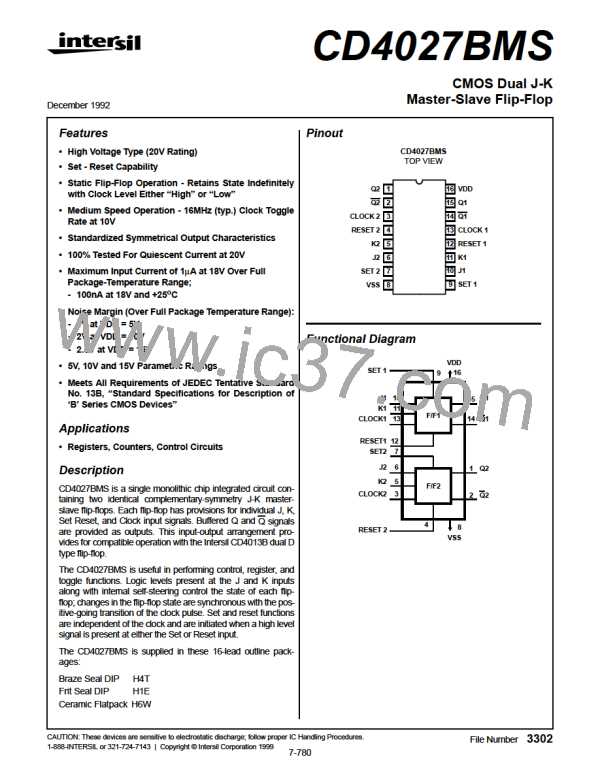

CD4027BMS

TABLE 8. BURN-IN AND IRRADIATION TEST CONNECTIONS

OSCILLATOR

50kHz 25kHz

FUNCTION

OPEN

GROUND

VDD

9V ± -0.5V

Static Burn-In 1

Note 1

1, 2, 14, 15

3 - 13

16

Static Burn-In 2

Note 1

1, 2, 14, 15

-

8

4, 7 - 9, 12

8

3 - 7, 9 - 13, 16

5, 6, 10, 11, 16

3 - 7, 9 - 13, 16

Dynamic Burn-

In Note 2

12, 14, 15

3, 13

Irradiation

Note 3

1, 2, 14, 15

NOTE:

1. Each pin except VDD and GND will have a series resistor of 10K ± 5%, VDD = 18V ± 0.5V

2. Each pin except VDD and GND will have a series resistor of 4.75K ± 5%, VDD = 18V ± 0.5V

3. Each pin except VDD and GND will have a series resistor of 47K ± 5%; Group E, Subgroup 2, sample size is 4 dice/wafer, 0 failures,

VDD = 10V ± 0.5V

Logic Diagram

RESET

*4(12)

Q

CL

p

CL

p

2(14)

1(15)

J

MASTER

*6(10)

*5(11)

SLAVE

Q

TG

n

TG

n

K

CL

p

CL

p

CL

CL

TG

n

TG

n

VDD

SET

CL

CL

*7(9)

CL

CL

* ALL INPUTS ARE

PROTECTED BY

CMOS PROTECTION

NETWORK

*3(13)

CLOCK

VSS

LOGIC DIAGRAM AND TRUTH TABLE FOR CD4027BMS (ONE OF TWO IDENTICAL J-K FLIP-FLOPS)

TRUTH TABLE

PRESENT STATE

INPUTS

NEXT STATE

OUTPUT

OUTPUTS

J

1

K

X

0

S

0

0

0

0

0

1

0

1

R

0

0

0

0

0

0

1

1

Q

0

CL*

Q

1

1

0

0

Q

0

0

1

1

X

0

1

X

1

0

X

X

X

X

X

1

X

X

X

X

X

X

X

X

No Change

X

X

X

1

0

1

0

1

1

Logic 1 = High Level

Logic 0 = Low Level

* = Level change

X = Don’t care

7-785

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]