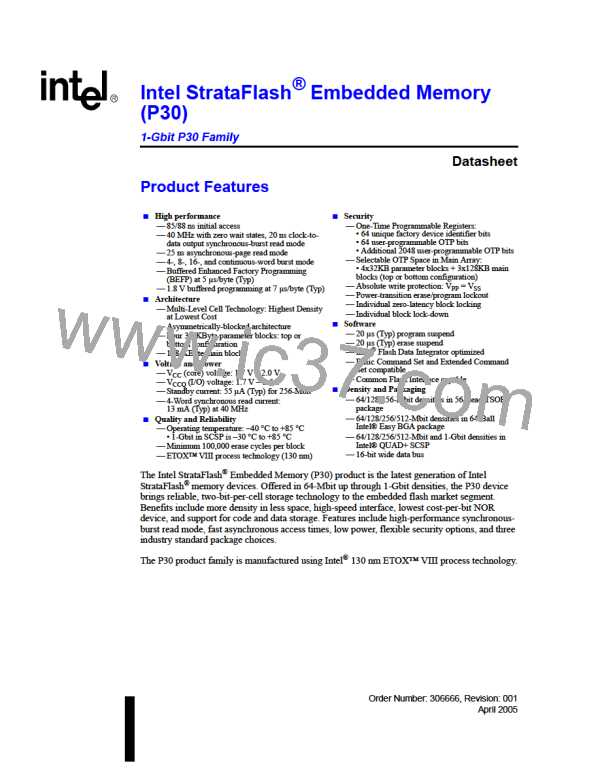

1-Gbit P30 Family

SR[5]. If a command sequence error occurs during an erase suspend, SR[4] and SR[5] remains set,

even after the erase operation is resumed. Unless the Status Register is cleared using the Clear

Status Register command before resuming the erase operation, possible erase errors may be

masked by the command sequence error.

If a block is locked or locked-down during an erase suspend of the same block, the lock status bits

change immediately. However, the erase operation completes when it is resumed. Block lock

operations cannot occur during a program suspend. See Appendix A, “Write State Machine” on

page 78, which shows valid commands during an erase suspend.

13.2

Selectable One-Time Programmable Blocks

Any of four pre-defined areas from the main array (the four 32 KB parameter blocks together as

one and the three adjacent 128 KB main blocks) can be configured as One-Time Programmable

(OTP) so further program and erase operations are not allowed. This option is available for top or

bottom parameter devices.

Table 27.

Selectable OTP Block Mapping

Density

Top Parameter Configuration

Bottom Parameter Configuration

blocks 258:255 (parameters)

block 254 (main)

blocks 3:0 (parameters)

block 4 (main)

256-Mbit

block 253 (main)

block 5 (main)

block 252 (main)

block 6 (main)

blocks 130:127 (parameters)

block 126 (main)

blocks 3:0 (parameters)

block 4 (main)

128-Mbit

block 125 (main)

block 5 (main)

block 124 (main)

block 6 (main)

blocks 66:63 (parameters)

block 62 (main)

blocks 3:0 (parameters)

block 4 (main)

64-Mbit

block 61 (main)

block 5 (main)

block 60 (main)

block 6 (main)

Note: The 512-Mbit and 1-Gbit devices will have multiple Selectable OTP Areas depending on

the number of 256-Mbit dies in the stack and the placement of the parameter blocks.

Please see your local Intel representative for details about the Selectable OTP implementation.

Datasheet

Intel StrataFlash® Embedded Memory (P30)

Order Number: 306666, Revision: 001

April 2005

71

INTEL [ INTEL ]

INTEL [ INTEL ]