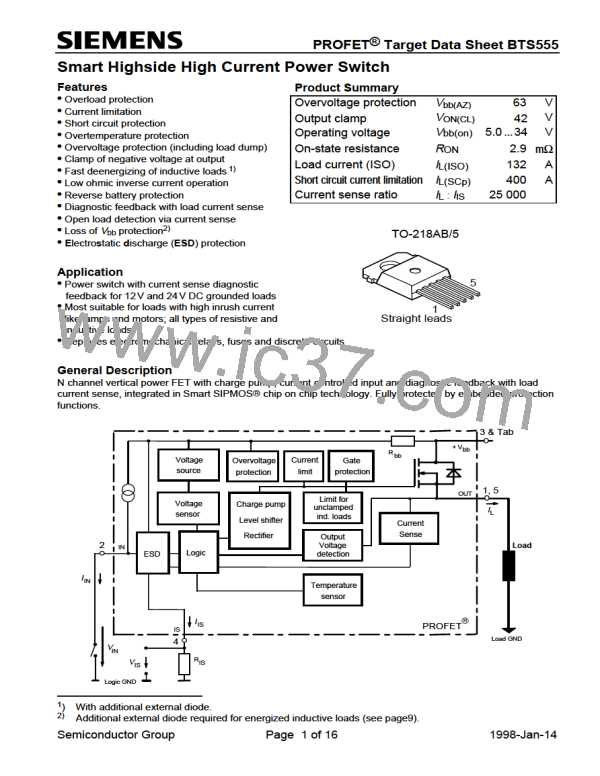

Target Data Sheet BTS555

Timing diagrams

Figure 2b: Switching an inductive load:

Figure 1a: Switching a resistive load,

change of load current in on-condition:

IIN

IIN

VOUT

dV/dtoff

VOUT

90%

t

on

dV/dton

t

off

t

10%

t

IL

slc(IS)

slc(IS)

IL

Load 1

Load 2

IIS

t

IIS

t

son(IS)

t

t

soff(IS)

The sense signal is not valid during a settling time

after turn-on/off and after change of load current.

Figure 3a: Short circuit:

shut down by short circuit detection, reset by I =0.

IN

Figure 2a: Switching motors and lamps:

IIN

IIN

IL

IL(SCp)

VOUT

td(SC)

IIL

I

IS

VOUT>>0

VOUT=0

t

IIS

t

Shut down remains latched until next reset via input.

Sense current saturation can occur at very high

inrush currents (see IIS,lim on page 6).

Semiconductor Group

Page 13

1998-Jan-14

INFINEON [ Infineon ]

INFINEON [ Infineon ]