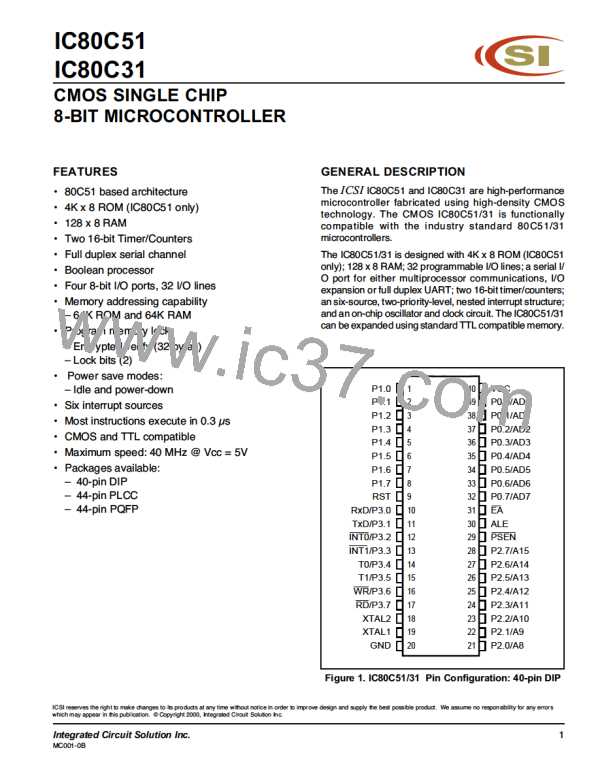

IC80C51

IC80C31

ROM Verification

The address of the program menory location to be read is

applied to Port 1 and pins P2.3-P2.0. The other pins should

be held at the “Verify” level . The contents of the addressed

locations will be emitted on Port 0. External pullups are

required on Rort 0 for this operation. Figure 23 shows the

setup to verify the program memory.

+ 5V

A7-A0

P1

Vcc

10K x 8

A11-A8

P2.3-P2.0

1

1

1

0

0

0

RST

EA

ALE

PSEN

P2.7

P2.6

PGM

DATA

P0

XTAL1

4-6 MHz

XTAL2

GND

Figure 23. ROM Verification

Integrated Circuit Solution Inc.

MC001-0B

35

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]