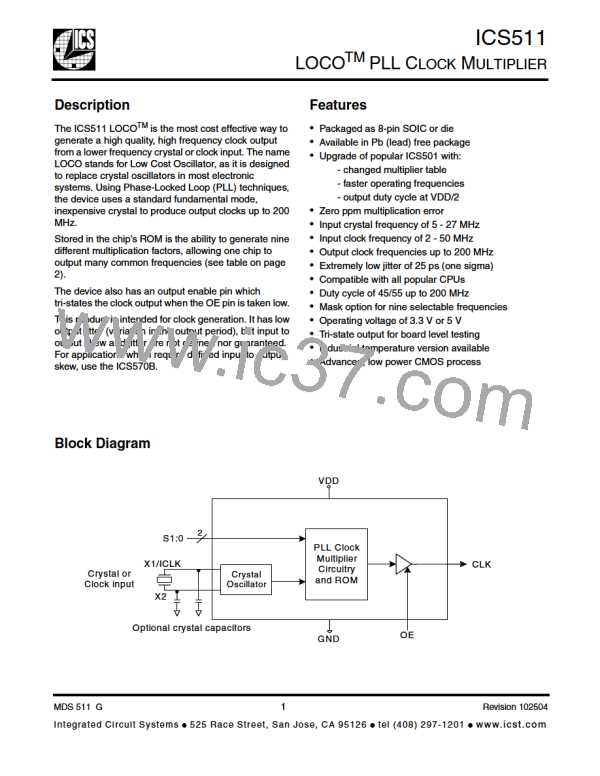

ICS511

TM

LOCO PLL Clock Multiplier

Package Outline and Package Dimensions (8-pin SOIC, 150 Mil. Narrow Body)

Package dimensions are kept current with JEDEC Publication No. 95

8

Millimeters

Inches

Symbol

Min

Max

1.75

0.25

0.51

0.25

5.00

4.00

Min

Max

A

A1

B

C

D

E

e

1.35

0.10

0.33

0.19

4.80

3.80

.0532

.0040

.013

.0075

.1890

.1497

.0688

.0098

.020

.0098

.1968

.1574

E

H

INDEX

AREA

1.27 BASIC

0.050 BASIC

1

2

H

h

L

5.80

6.20

0.50

1.27

8°

.2284

.010

.016

0°

.2440

.020

.050

8°

0.25

0.40

0°

D

α

A

h x 45

A1

C

- C -

e

SEATING

PLANE

B

L

.10 (.004)

C

MDS 511 G

7

Revision 102504

Integrated Circuit Systems ● 525 Race Street, San Jose, CA 95126 ● tel (408) 297-1201 ● www.icst.com

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]