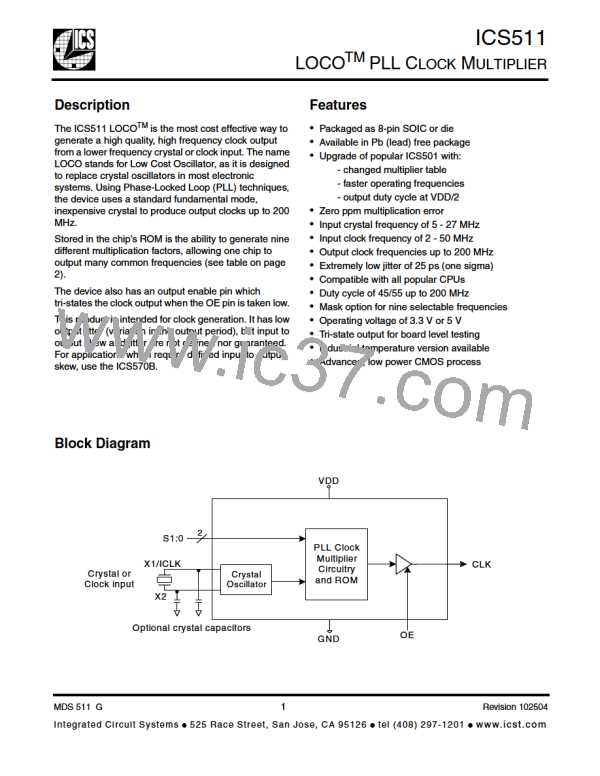

ICS511

TM

LOCO PLL Clock Multiplier

DC Electrical Characteristics

VDD=3.3 V 5% , Ambient temperature -40 to +85°C, unless stated otherwise

Parameter

Symbol Conditions

Min.

3.135

Typ.

Max.

Units

Operating Voltage

VDD

3.465

V

V

Input High Voltage, ICLK only

Input Low Voltage, ICLK only

Input High Voltage

V

ICLK (pin 1)

ICLK (pin 1)

OE (pin 7)

OE (pin 7)

S0, S1

(VDD/2)+0.7

IH

V

(VDD/2)-0.7

V

IL

V

2.0

VDD-0.5

2.4

V

IH

Input Low Voltage

V

0.8

0.5

0.4

V

IL

Input High Voltage

V

V

IH

Input Low Voltage

V

S0, S1

V

IL

Output High Voltage

Output Low Voltage

V

I

I

= -25 mA

= 25 mA

V

OH

OH

OL

V

V

OL

IDD Operating Supply Current,

20 MHz crystal

No load, 100M

8

mA

Short Circuit Current

CLK output

Pin 7

+70

270

4

mA

kΩ

pF

Ω

On-Chip Pull-up Resistor

Input Capacitance, S1, S0, and OE

Nominal Output Impedance

Pins 4, 6, 7

20

AC Electrical Characteristics

VDD = 3.3 V 5%, Ambient Temperature -40 to +85° C, unless stated otherwise

Parameter

Input Frequency, crystal input

Input Frequency, clock input

Output Frequency

Symbol

Conditions

Min.

5

Typ.

Max. Units

F

F

27

50

MHz

MHz

MHz

MHz

ns

IN

2

IN

F

0°C to +70°C

14

14

160

145

OUT

-40°C to +85°C

Output Clock Rise Time

Output Clock Fall Time

Output Clock Duty Cycle

PLL Bandwidth

t

0.8 to 2.0 V, Note 1

2.0 to 8.0 V, Note 1

1.5 V, up to 160 MHz

1

1

OR

t

ns

OF

t

45

10

49-51

55

%

OD

kHz

ns

Output Enable Time, OE high to

output on

50

50

Output Disable Time, OE low to

tri-state

ns

Absolute Clock Period Jitter

One Sigma Clock Period Jitter

t

t

Deviation from mean

+70

25

ps

ps

ja

js

Note 1: Measured with 15 pF load.

MDS 511 G

4

Revision 102504

Integrated Circuit Systems ● 525 Race Street, San Jose, CA 95126 ● tel (408) 297-1201 ● www.icst.com

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]