HT46R01B/02B/01N/02N

HT48R01B/02B/01N/02N

·

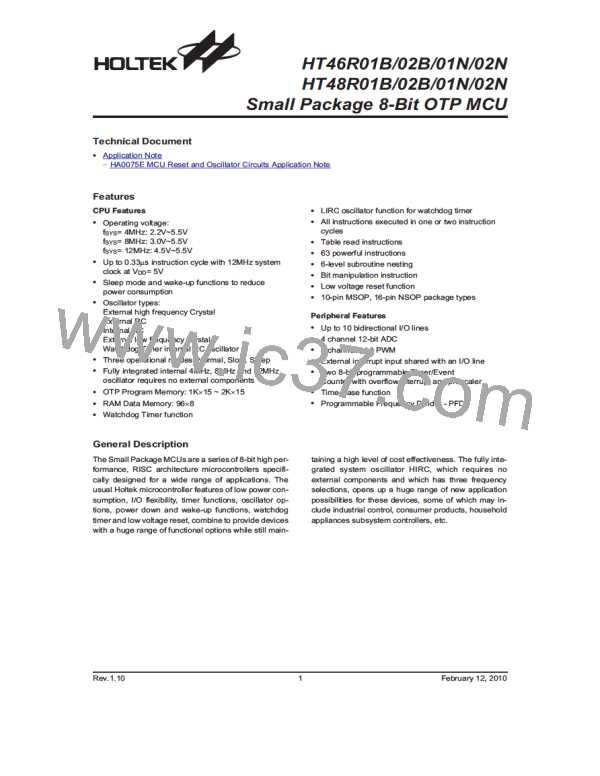

TMR1C Register

Bit

7

6

T1M0

R/W

0

5

4

T1ON

R/W

0

3

T1EG

R/W

1

2

1

0

Name

R/W

T1M1

R/W

0

T1S

R/W

0

¾

¾

¾

¾

¾

¾

¾

¾

¾

POR

Bit 7,6

T1M1, T1M0: Timer 1 Operation mode selection

00: no mode available

01: event counter mode

10: timer mode

11: pulse width capture mode

Bit 5

Bit 4

T1S: timer clock source

0: fSYS/4

1: LXT oscillator

T1ON: Timer/event counter counting enable

0: disable

1: enable

Bit 3

T1EG:

Event counter active edge selection

0: count on raising edge

1: count on falling edge

Pulse Width Capture active edge selection

0: start counting on falling edge, stop on rasing edge

1: start counting on raising edge, stop on falling edge

Bit 2~0

unimplemented, read as ²0²

Rev.1.10

35

February 12, 2010

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]