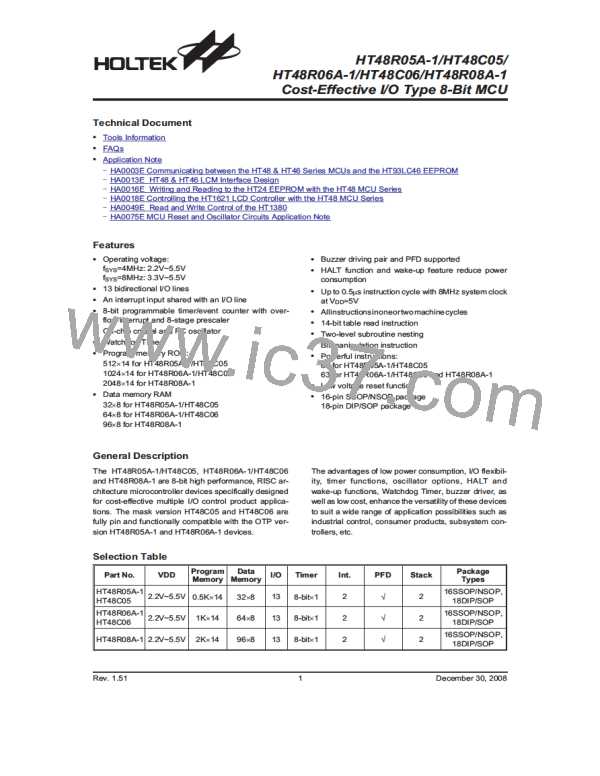

HT48R05A-1/HT48C05/HT48R06A-1/HT48C06/HT48R08A-1

Test Conditions

Symbol

Parameter

Min.

Typ.

Max.

Unit

VDD

3V

5V

3V

5V

Conditions

5

10

1

¾

¾

¾

¾

¾

¾

¾

¾

mA

mA

ISTB1

Standby Current (WDT Enabled)

Standby Current (WDT Disabled)

No load, system HALT

ISTB2

No load, system HALT

mA

2

Input Low Voltage for I/O Ports,

TMR and INT

VIL1

0.3VDD

0

V

V

¾

¾

¾

¾

¾

¾

Input High Voltage for I/O Ports,

TMR and INT

VIH1

0.7VDD

VDD

VIL2

0.4VDD

VDD

Input Low Voltage (RES)

Input High Voltage (RES)

Low Voltage Reset

0

0.9VDD

2.7

V

V

V

¾

¾

¾

¾

¾

¾

3.0

8

VIH2

VLVR

LVRenabled

3.3

¾

3V

5V

3V

5V

3V

5V

4

¾

¾

IOL

V

V

OL=0.1VDD

OH=0.9VDD

I/O Port Sink Current

I/O Port Source Current

Pull-high Resistance

mA

mA

kW

10

20

-2

-5

20

10

-4

-10

60

¾

IOH

¾

100

50

RPH

¾

30

A.C. Characteristics

Ta=25°C

Test Conditions

Conditions

Symbol

Parameter

Min.

Typ.

Max.

Unit

VDD

¾

2.2V~5.5V

3.3V~5.5V

2.2V~5.5V

3.3V~5.5V

400

400

0

4000

8000

4000

8000

180

130

46

kHz

kHz

kHz

kHz

¾

¾

¾

¾

90

65

23

17

fSYS

System Clock (Crystal OSC, RC OSC)

¾

¾

fTIMER

Timer I/P Frequency (TMR)

Watchdog Oscillator Period

Watchdog Time-out Period (RC)

0

¾

3V

5V

3V

5V

45

32

11

8

tWDTOSC

¾

ms

tWDT1

Without WDT prescaler

Without WDT prescaler

ms

33

Watchdog Time-out Period

(System Clock)

tWDT2

tSYS

1024

¾

¾

¾

tRES

tSST

tINT

External Reset Low Pulse Width

System Start-up Timer Period

Interrupt Pulse Width

1

¾

¾

¾

¾

¾

¾

¾

1024

¾

¾

¾

¾

2

ms

tSYS

Wake-up from HALT

1

¾

¾

ms

tLVR

Low Voltage Width to Reset

0.25

1

ms

Note: tSYS=1/fSYS

Rev. 1.51

4

December 30, 2008

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]