HT46R23/HT46C23

S

t

a

r

t

S

l

a

v

e

A

d

d

r

e

s

s

S

R

W

A

C

K

S

C

L

0

1

1

1

0

1

0

1

0

S

D

A

D

a

t

a

A

C

K

S

t

o

p

S

C

L

1

0

0

1

0

1

0

0

S

D

A

S

S

S

M

D

A

P

=

A

R

S

t

S

a

r

t

(

1

b

i

t

)

=

l

a

v

e

A

d

d

r

e

s

s

(

7

b

i

t

s

)

=

S

R

W

b

i

t

(

1

b

i

t

)

=

S

l

a

v

e

d

e

v

i

c

e

s

e

n

d

a

c

k

n

o

w

l

e

d

g

e

b

i

t

(

1

b

i

t

)

=

D

a

t

a

(

8

b

i

t

s

)

=

=

A

S

C

t

K

(

R

X

A

i

K

b

i

t

f

o

r

t

r

a

n

s

m

i

t

t

e

r

,

T

X

A

K

b

i

t

f

o

r

r

e

c

e

i

v

e

r

1

b

i

t

)

o

p

(

1

b

t

)

S

S

A

S

R

M

D

A

D

A

S

S

A

S

R

M

D

A

D

A

P

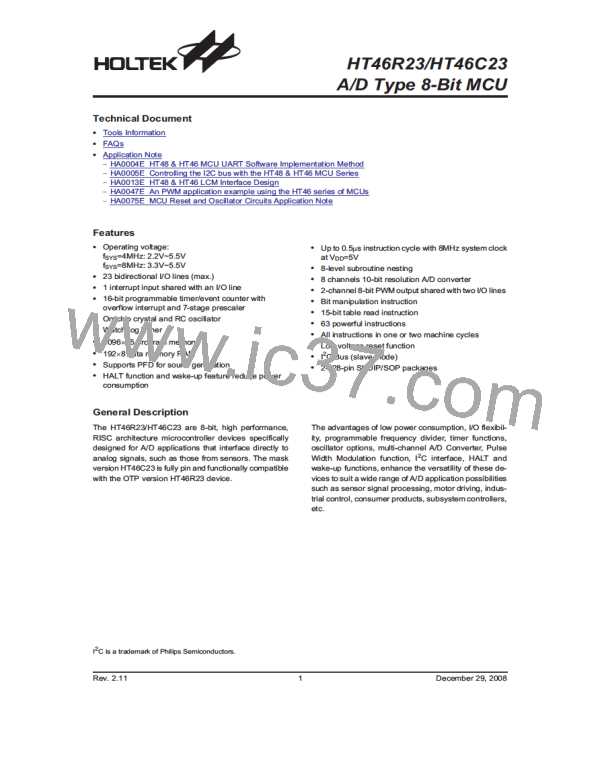

I2C Communication Timing Diagram

Start Signal

In interrupt subroutine, check HAAS bit to know whether

the I2C Bus interrupt comes from a slave address that is

matched or a data byte transfer is completed. When the

slave address is matched, the device must be in trans-

mit mode or receive mode and write data to HDR or

dummy read from HDR to release the SCL line.

The START signal is generated only by the master de-

vice. The other device in the bus must detect the START

signal to set the I2C Bus busy bit (HBB). The START sig-

nal is SDA line from high to low, when SCL is high.

S

C

L

SRW Bit

The SRW bit means that the master device wants to

read from or write to the I2C Bus. The slave device

check this bit to understand itself if it is a transmitter or a

receiver. The SRW bit is set to ²1² means that the mas-

ter wants to read data from the I2C Bus, so the slave de-

vice must write data to a bus as a transmitter. The SRW

is cleared to ²0² means that the master wants to write

data to the I2C Bus, so the slave device must read data

from the I2C Bus as a receiver.

S

D

A

Start Bit

Slave Address

The master must select a device for transferring the

data by sending the slave device address after the

START signal. All device in the I2C Bus will receive the

I2C Bus slave address (7 bits) to compare with its own

slave address (7 bits). If the slave address is matched,

the slave device will generate an interrupt and save the

following bit (8th bit) to SRW bit and sends an acknowl-

edge bit (low level) to the 9th bit. The slave device also

sets the status flag (HAAS), when the slave address is

matched.

Rev. 2.11

24

December 29, 2008

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]