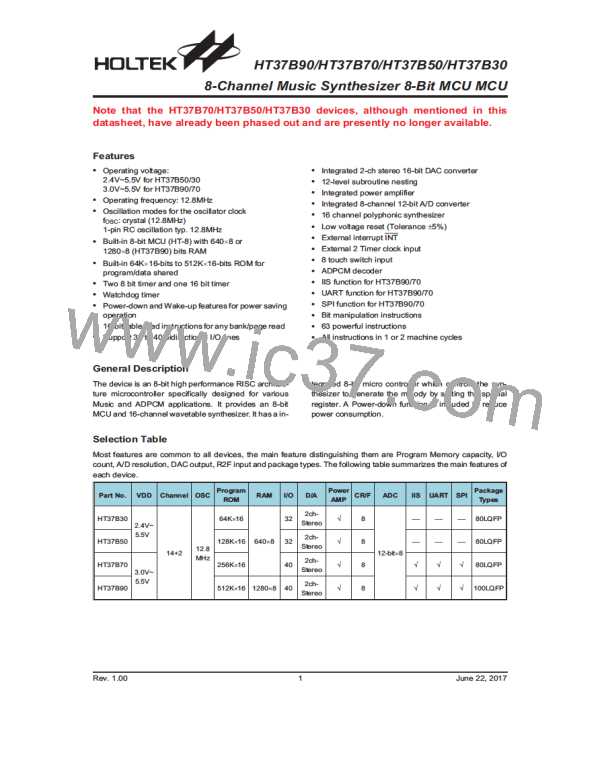

HT37B90/HT37B70/HT37B50/HT37B30

IIS Function

D/A Converter Interface

the right channel, and a ²L² state is used for the left

channel.

The device provides the IIS serial data format to support

the multiple D/A converters, one bit clock output and a

word clock signal for left/right stereo serial data trans-

mission.

CK Description

CK bit clock is the clock source for the signal. which can

accept the IIS serial data format.

Clock Signal

DT:Stereo Serial Data Format Transmit

The bit clock output signals DCK are used to synchro-

nize the IIS serial data. The word clock signal LOAD di-

vides the serial data into left channel and right channel

data for two-way audio output.

The audio output data is in serial mode with 16 bit digital

signal and LSB first output. There is a high sampling

rate of 50kHz when the fOSC is 12.8MHz and with two

channel outputs for Right/Left channel. The device pro-

vides only one serial data format as IIS mode. The user

could directly connect a D/A converter which can accept

the IIS serial data format.

WAS Description

The word clock signal WAS is used for IIS serial data.

The stereo serial data consists of 16-channel sound

generator. On IIS format, a ²H² state on WAS is used for

D/A Converter Timing

UART Bus Serial Interface

The device contains an integrated full-duplex asynchronous serial communications. The UART function can transmit

and receive data serially by transferring a frame of data with eight per transmission. The UART function possesses its

own internal interrupt which can be used to indicate when a reception occurs or when a transmission terminates. If the

UART Clock always generates 31.25kHz, the value of BRGR should correspond to fOSC

.

Register Name

RS232C

TXD

Bit7

¾

Bit6

¾

Bit5

PH

D5

Bit4

EN

D4

Bit3

¾

Bit2

Bit1

BE

D1

Bit0

BF

¾

D2

D2

D7

D7

D6

D6

D3

D3

D0

RXD

D5

D4

D1

D0

Note:

¾: No function, read only, read as 0.

BF: RX buffer full; 0: Buffer not full; 1: Buffer full (Default=0)

BE: TX buffer empty; 0: Buffer not empty; 1: Buffer empty (Default=1)

EN: Enable/disable RS232 function; 0: disable; 1: enable

PH: RS232 input Pull High control (Default=1)

0= disable; 1= enable

BRGR

Decimal

Bit7

Integer

Prescaler

Bit6

1

Bit5

0

Bit4

0

Bit3

0

Bit2

0

Bit1

Bit0

1

1

0

0

0

1

0

2

1

1

0

0

0

Rev. 1.00

60

June 22, 2017

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]