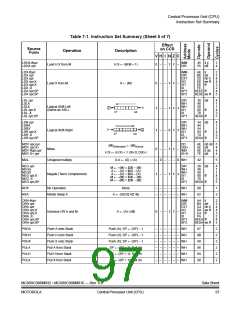

Table 7-2. Opcode Map

Bit Manipulation Branch

Read-Modify-Write

Control

Register/Memory

DIR

DIR

REL

DIR

3

INH

4

INH

IX1

SP1

9E6

IX

7

INH

INH

IMM

A

DIR

B

EXT

C

IX2

SP2

IX1

E

SP1

9EE

IX

F

MSB

0

1

2

5

6

8

9

D

9ED

LSB

5

4

3

4

1

NEGA

INH

1

NEGX

INH

4

5

3

7

3

2

3

4

4

5

3

4

2

0

BRSET0 BSET0

BRA

NEG

NEG

NEG

NEG

RTI

BGE

SUB

SUB

SUB

SUB

SUB

SUB

SUB

SUB

3

DIR

5

2

DIR

4

2

2

2

2

2

2

2

2

REL 2 DIR

3

BRN

REL 3 DIR

3

BHI

REL

3

BLS

REL 2 DIR

3

BCC

REL 2 DIR

3

BCS

REL 2 DIR

3

BNE

REL 2 DIR

3

BEQ

1

1

2

IX1 3 SP1 1 IX

5

1

1

INH

4

RTS

INH

2

2

2

2

1

1

REL 2 IMM 2 DIR

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

EXT 3 IX2

4

CMP

EXT 3 IX2

4

SBC

EXT 3 IX2

4

CPX

EXT 3 IX2

4

AND

EXT 3 IX2

4

BIT

EXT 3 IX2

4

LDA

EXT 3 IX2

4

STA

EXT 3 IX2

4

EOR

EXT 3 IX2

4

ADC

EXT 3 IX2

4

ORA

EXT 3 IX2

4

ADD

EXT 3 IX2

3

JMP

EXT 3 IX2

5

JSR

4

4

4

4

4

4

4

4

4

4

4

4

SP2 2 IX1

5

CMP

SP2 2 IX1

5

SBC

SP2 2 IX1

5

CPX

SP2 2 IX1

5

AND

SP2 2 IX1

5

BIT

SP2 2 IX1

5

LDA

SP2 2 IX1

5

STA

SP2 2 IX1

5

EOR

SP2 2 IX1

5

ADC

SP2 2 IX1

5

ORA

SP2 2 IX1

5

ADD

SP2 2 IX1

3

3

3

3

3

3

3

3

3

3

3

3

SP1 1 IX

4

CMP

SP1 1 IX

4

SBC

SP1 1 IX

4

CPX

SP1 1 IX

4

AND

SP1 1 IX

4

BIT

SP1 1 IX

4

LDA

SP1 1 IX

4

STA

SP1 1 IX

4

EOR

SP1 1 IX

4

ADC

SP1 1 IX

4

ORA

SP1 1 IX

4

ADD

SP1 1 IX

5

4

4

6

4

2

3

4

3

2

1

2

BRCLR0 BCLR0

CBEQ CBEQA CBEQX CBEQ

CBEQ

CBEQ

BLT

CMP

CMP

CMP

CMP

CMP

3

DIR

5

2

DIR

4

3

IMM 3 IMM 3 IX1+

4

SP1 2 IX+

REL 2 IMM 2 DIR

5

7

3

2

DAA

3

BGT

2

SBC

3

SBC

4

SBC

3

SBC

2

SBC

BRSET1 BSET1

MUL

INH

DIV

INH

NSA

3

DIR

5

2

DIR

4

1

1

1

2

2

3

2

2

2

2

2

INH

1

INH

3

REL 2 IMM 2 DIR

3

4

1

1

4

COM

IX1

4

LSR

IX1

3

CPHX

IMM

4

ROR

IX1

4

ASR

IX1

4

LSL

IX1

4

ROL

IX1

4

DEC

IX1

5

9

2

CPX

3

CPX

4

CPX

3

CPX

2

CPX

3

BRCLR1 BCLR1

COM

COMA

COMX

COM

COM

SWI

BLE

3

DIR

5

2

DIR

4

1

INH

1

INH

3

3

SP1 1 IX

1

1

1

1

1

1

1

1

1

1

INH

REL 2 IMM 2 DIR

4

LSR

1

LSRA

INH

1

LSRX

INH

5

LSR

SP1 1 IX

3

LSR

2

2

2

AND

IMM 2 DIR

2

BIT

IMM 2 DIR

2

LDA

IMM 2 DIR

2

AIS

IMM 2 DIR

2

EOR

IMM 2 DIR

2

ADC

IMM 2 DIR

3

AND

4

AND

3

AND

2

AND

4

BRSET2 BSET2

TAP

TXS

3

DIR

5

2

DIR

4

1

3

1

INH

INH

2

2

2

2

2

2

2

2

4

3

4

4

1

2

3

BIT

4

BIT

3

BIT

2

BIT

5

BRCLR2 BCLR2

STHX

LDHX

LDHX

CPHX

TPA

TSX

3

DIR

5

2

DIR

4

IMM 2 DIR

2

DIR

3

INH

INH

4

ROR

1

1

5

2

PULA

INH

2

PSHA

INH

2

PULX

INH

2

PSHX

INH

2

PULH

INH

2

PSHH

INH

1

CLRH

INH

3

LDA

4

LDA

3

LDA

2

LDA

6

BRSET3 BSET3

RORA

RORX

ROR

SP1 1 IX

5

ASR

SP1 1 IX

5

LSL

SP1 1 IX

5

ROL

SP1 1 IX

5

DEC

SP1 1 IX

ROR

3

DIR

5

2

DIR

4

1

INH

1

INH

3

3

3

3

3

4

3

3

4

ASR

1

ASRA

INH

1

LSLA

INH

1

ROLA

INH

1

DECA

INH

1

ASRX

INH

1

LSLX

INH

1

ROLX

INH

1

DECX

INH

3

ASR

1

3

STA

4

STA

3

STA

2

STA

7

BRCLR3 BCLR3

TAX

3

DIR

5

2

DIR

4

REL 2 DIR

3

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

INH

4

LSL

3

LSL

1

CLC

INH

1

3

EOR

4

EOR

3

EOR

2

EOR

8

BRSET4 BSET4 BHCC

3

DIR

5

2

DIR

4

2

REL 2 DIR

3

4

ROL

3

ROL

3

ADC

4

ADC

3

ADC

2

ADC

9

BRCLR4 BCLR4 BHCS

SEC

INH

2

CLI

INH

2

SEI

INH

1

RSP

INH

3

DIR

5

2

DIR

4

2

2

2

2

2

2

2

REL 2 DIR

3

BPL

REL 2 DIR

3

BMI

REL 3 DIR

3

BMC

REL 2 DIR

3

BMS

REL 2 DIR

3

BIL

4

DEC

3

DEC

2

ORA

IMM 2 DIR

2

ADD

IMM 2 DIR

3

ORA

4

ORA

3

ORA

2

ORA

A

B

C

D

E

F

BRSET5 BSET5

3

DIR

5

2

DIR

4

5

3

3

5

6

4

3

ADD

4

ADD

3

ADD

2

ADD

BRCLR5 BCLR5

DBNZ DBNZA DBNZX DBNZ

DBNZ

DBNZ

3

DIR

5

2

DIR

4

2

1

1

3

1

INH

1

2

1

1

2

1

INH

1

3

2

2

3

2

IX1

4

INC

IX1

3

TST

IX1

4

MOV

IMD

3

CLR

IX1

SP1 2 IX

5

4

INC

3

INC

IX

2

TST

2

JMP

DIR

4

JSR

4

JMP

3

JMP

IX1

5

JSR

IX1

3

LDX

2

BRSET6 BSET6

INCA

INCX

INC

SP1

4

TST

JMP

3

DIR

5

2

DIR

4

INH

1

TSTA

INH

5

MOV

DD

1

CLRA

INH

INH

1

TSTX

INH

4

MOV

DIX+

1

CLRX

INH

1

2

2

2

1

1

IX

3

TST

1

4

BSR

REL 2 DIR

2

LDX

IMM 2 DIR

2

AIX

IMM 2 DIR

6

JSR

4

JSR

IX

2

LDX

BRCLR6 BCLR6

NOP

3

DIR

5

2

DIR

4

SP1 1 IX

INH

2

2

2

EXT 3 IX2

4

LDX

EXT 3 IX2

4

STX

EXT 3 IX2

4

1

STOP

INH

1

WAIT

INH

3

LDX

4

LDX

5

LDX

4

LDX

BRSET7 BSET7

MOV

*

1

TXA

INH

3

DIR

5

2

DIR

4

REL

3

BIH

2

IX+D

1

1

4

4

SP2 2 IX1

5

3

3

SP1 1 IX

4

3

CLR

4

CLR

SP1 1 IX

2

CLR

3

STX

4

STX

3

STX

2

STX

BRCLR7 BCLR7

DIR DIR

STX

SP2 2 IX1

STX

SP1 1 IX

3

2

REL 2 DIR

3

1

INH Inherent

REL Relative

SP1 Stack Pointer, 8-Bit Offset

SP2 Stack Pointer, 16-Bit Offset

IX+ Indexed, No Offset with

Post Increment

IX1+ Indexed, 1-Byte Offset with

Post Increment

MSB

LSB

0

High Byte of Opcode in Hexadecimal

Cycles

IMM Immediate

DIR Direct

IX

Indexed, No Offset

IX1 Indexed, 8-Bit Offset

IX2 Indexed, 16-Bit Offset

IMD Immediate-Direct

EXT Extended

DD Direct-Direct

IX+D Indexed-Direct DIX+ Direct-Indexed

*Pre-byte for stack pointer indexed instructions

5

Low Byte of Opcode in Hexadecimal

0

BRSET0 Opcode Mnemonic

DIR Number of Bytes / Addressing Mode

3

FREESCALE [ Freescale ]

FREESCALE [ Freescale ]