(4)

(1) Normal

operation

YES

V

<12 V?

DD

NO

N

NO

<=12 V?

O

(2)

(5)

(6)

YES

I >2/3I

?

PK

P

Timing=1700 ms

V

DD

SCP

(3)

Timing =100

OCP

SCP

(7) Gate off

ms

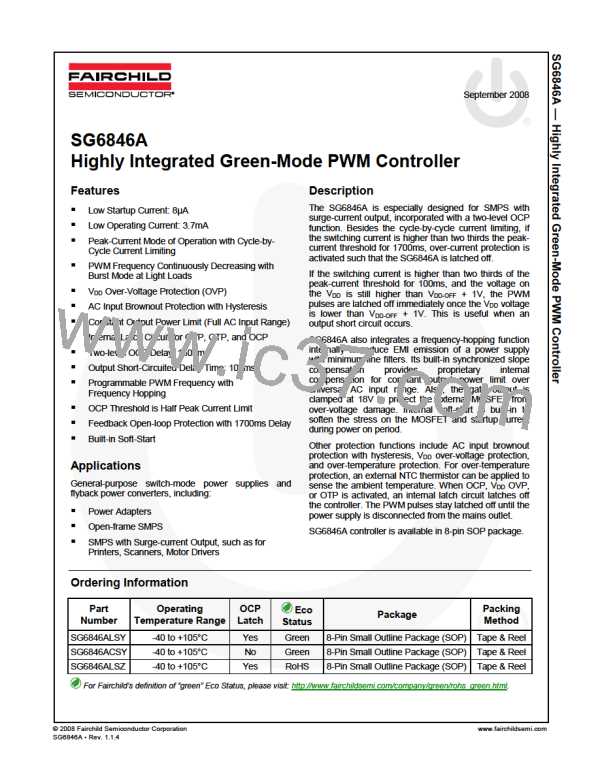

Figure 6. SG6846A OCP/SCP Logic Flow Diagram

Electrical Characteristics (Continued)

VDD = 15V and TA = 25°C unless otherwise noted.

Symbol

Parameter

Test Condition

Min.

Typ. Max.

Unit

Oscillator Section

Center

Frequency

62

±3.7

124

65

±4.2

130

68

±4.7

136

fOSC

Normal PWM Frequency

RI = 26kꢀ, VFB>VN

RI = 13kꢀ, VFB>VN

RI = 36kꢀ, VFB>VN

kHz

kHz

Jitter Range

Center

Frequency

Maximum PWM

Frequency

fOSC,MAX

±7.4

44.8

±2.54

±8.4

47.0

±2.90

±9.4

49.2

±3.26

Jitter Range

Center

Frequency

fOSC,MIN

Minimum PWM Frequency

Jitter Period

kHz

ms

Jitter Range

thop-1

thop-3

3.9

10.2

18.0

1.9

4.4

11.5

22.5

2.1

4.9

12.8

25.0

2.3

RI = 26kꢀ, VFB ≥ VN

RI = 26kꢀ, VFB = VG

RI = 26kꢀ

fOSC-G

Green-Mode Minimum Frequency

kHz

V

Pin, FB voltage

FB Pin Frequency

VFB-N

RI = 26kꢀ, VFB = VN

RI = 26kꢀ, VFB = VG

Reduction Threshold

Jitter Range

Pin, FB voltage

Jitter Range

3.7

4.2

4.7

KHz

V

1.4

1.6

1.8

VFB-G

FB Voltage at fOSC-G

1.27

1.45

85

1.62

KHz

Hz/mV

%

SG

fDV

Slope for Green-Mode Modulation

RI = 26kꢀ

Frequency Variation vs. VDD Deviation

VDD = 11.5V to 20V

5

Frequency Variation vs. Temperature

Deviation

fDT

TA = -30 to 85°C

1.5

5.0

%

Continued on following page…

© 2008 Fairchild Semiconductor Corporation

SG6846A • Rev. 1.1.4

www.fairchildsemi.com

7

FAIRCHILD [ FAIRCHILD SEMICONDUCTOR ]

FAIRCHILD [ FAIRCHILD SEMICONDUCTOR ]