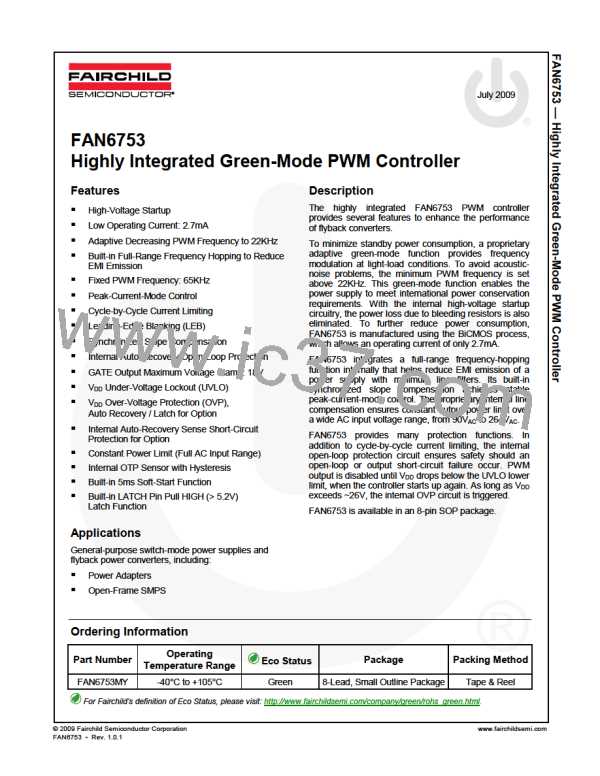

Physical Dimensions

5.00

4.80

A

0.65

3.81

8

5

B

1.75

6.20

5.80

4.00

3.80

5.60

1

4

PIN ONE

INDICATOR

1.27

1.27

(0.33)

M

0.25

C B A

LAND PATTERN RECOMMENDATION

SEE DETAIL A

0.25

0.10

0.25

0.19

C

1.75 MAX

0.10

C

0.51

0.33

OPTION A - BEVEL EDGE

0.50

0.25

x 45°

R0.10

R0.10

GAGE PLANE

OPTION B - NO BEVEL EDGE

0.36

NOTES: UNLESS OTHERWISE SPECIFIED

8°

0°

0.90

A) THIS PACKAGE CONFORMS TO JEDEC

MS-012, VARIATION AA, ISSUE C,

B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS DO NOT INCLUDE MOLD

FLASH OR BURRS.

SEATING PLANE

(1.04)

0.406

D) LANDPATTERN STANDARD: SOIC127P600X175-8M.

E) DRAWING FILENAME: M08AREV13

DETAIL A

SCALE: 2:1

Figure 19. 8-Pin Small Outline Package (SOP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify

or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/.

© 2009 Fairchild Semiconductor Corporation

FAN6753 • Rev. 1.0.1

www.fairchildsemi.com

11

FAIRCHILD [ FAIRCHILD SEMICONDUCTOR ]

FAIRCHILD [ FAIRCHILD SEMICONDUCTOR ]