xr

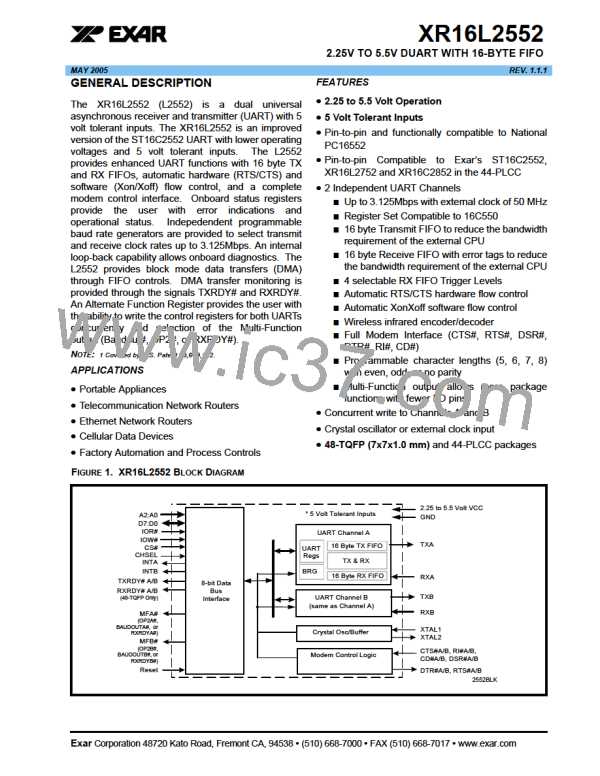

XR16L2552

2.25V TO 5.5V DUART WITH 16-BYTE FIFO

REV. 1.1.1

4.4.1 IER VERSUS RECEIVE FIFO INTERRUPT MODE OPERATION ............................................................................. 23

4.4.2 IER VERSUS RECEIVE/TRANSMIT FIFO POLLED MODE OPERATION................................................................ 24

4.5 INTERRUPT STATUS REGISTER (ISR) - READ-ONLY ............................................................................... 25

4.5.1 INTERRUPT GENERATION: ...................................................................................................................................... 25

4.5.2 INTERRUPT CLEARING: ........................................................................................................................................... 25

TABLE 9: INTERRUPT SOURCE AND PRIORITY LEVEL ....................................................................................................................... 26

4.6 FIFO CONTROL REGISTER (FCR) - WRITE-ONLY ..................................................................................... 26

TABLE 10: RECEIVE FIFO TRIGGER LEVEL SELECTION ................................................................................................................... 27

4.7 LINE CONTROL REGISTER (LCR) - READ/WRITE ..................................................................................... 27

TABLE 11: PARITY SELECTION ........................................................................................................................................................ 28

4.8 MODEM CONTROL REGISTER (MCR) OR GENERAL PURPOSE OUTPUTS CONTROL - READ/WRITE 28

4.9 LINE STATUS REGISTER (LSR) - READ ONLY ........................................................................................... 29

4.10 MODEM STATUS REGISTER (MSR) - READ ONLY .................................................................................. 30

4.11 SCRATCH PAD REGISTER (SPR) - READ/WRITE .................................................................................... 31

4.12 BAUD RATE GENERATOR REGISTERS (DLL AND DLM) - READ/WRITE .............................................. 31

4.13 ALTERNATE FUNCTION REGISTER (AFR) - READ/WRITE ..................................................................... 31

4.14 DEVICE IDENTIFICATION REGISTER (DVID) - READ ONLY .................................................................... 32

4.15 DEVICE REVISION REGISTER (DREV) - READ ONLY .............................................................................. 32

4.16 ENHANCED FEATURE REGISTER (EFR) .................................................................................................. 32

TABLE 12: SOFTWARE FLOW CONTROL FUNCTIONS........................................................................................................................ 33

4.17 SOFTWARE FLOW CONTROL REGISTERS (XOFF1, XOFF2, XON1, XON2) - READ/WRITE ................ 34

TABLE 13: UART RESET CONDITIONS FOR CHANNELS A AND B ......................................................................................... 35

TYPICAL PACKAGE THERMAL RESISTANCE DATA (MARGIN OF ERROR: ± 15%) ................................................ 35

ABSOLUTE MAXIMUM RATINGS ..................................................................................................................... 36

ELECTRICAL CHARACTERISTICS................................................................................ 36

DC ELECTRICAL CHARACTERISTICS.............................................................................................................. 36

AC ELECTRICAL CHARACTERISTICS.............................................................................................................. 37

FIGURE 14. CLOCK TIMING............................................................................................................................................................. 38

FIGURE 15. MODEM INPUT/OUTPUT TIMING FOR CHANNELS A & B ................................................................................................. 38

FIGURE 17. DATA BUS WRITE TIMING ............................................................................................................................................ 39

FIGURE 16. DATA BUS READ TIMING.............................................................................................................................................. 39

FIGURE 18. RECEIVE READY & INTERRUPT TIMING [NON-FIFO MODE] FOR CHANNELS A & B ......................................................... 40

FIGURE 19. TRANSMIT READY & INTERRUPT TIMING [NON-FIFO MODE] FOR CHANNELS A & B ....................................................... 40

FIGURE 20. RECEIVE READY & INTERRUPT TIMING [FIFO MODE, DMA DISABLED] FOR CHANNELS A & B........................................ 41

FIGURE 21. RECEIVE READY & INTERRUPT TIMING [FIFO MODE, DMA ENABLED] FOR CHANNELS A & B......................................... 41

FIGURE 22. TRANSMIT READY & INTERRUPT TIMING [FIFO MODE, DMA MODE DISABLED] FOR CHANNELS A & B ........................... 42

FIGURE 23. TRANSMIT READY & INTERRUPT TIMING [FIFO MODE, DMA MODE ENABLED] FOR CHANNELS A & B ............................ 42

PACKAGE DIMENSIONS (48 PIN TQFP - 7 X 7 X 1 MM) .............................................. 43

PACKAGE DIMENSIONS (44 PIN PLCC)....................................................................... 44

REVISION HISTORY ...................................................................................................................................... 45

TABLE OF CONTENTS ............................................................................................................ I

II

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]