xr

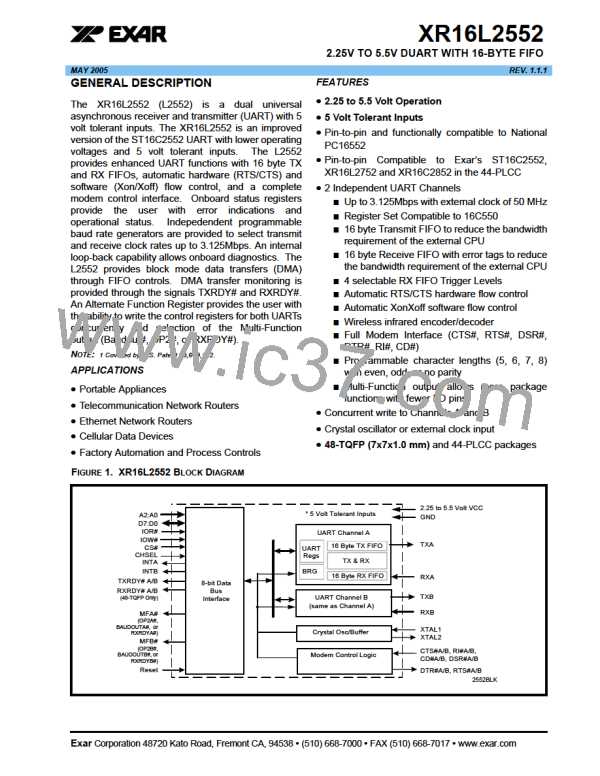

XR16L2552

2.25V TO 5.5V DUART WITH 16-BYTE FIFO

REV. 1.1.1

FIGURE 20. RECEIVE READY & INTERRUPT TIMING [FIFO MODE, DMA DISABLED] FOR CHANNELS A & B

Start

Bit

RX

S

S

S

S

T

D0:D7

D0:D7

D0:D7

T

D0:D7

TSSI

D0:D7

S

T

S

D0:D7

T

D0:D7

T

Stop

Bit

RX FIFO drops

below RX

Trigger Level

INT

TSSR

FIFO

Empties

RX FIFO fills up to RX

Trigger Level or RX Data

Timeout

RXRDY#

First Byte is

Received in

RX FIFO

TRRI

TRR

IOR#

(Reading data out

of RX FIFO)

RXINTDMA#

FIGURE 21. RECEIVE READY & INTERRUPT TIMING [FIFO MODE, DMA ENABLED] FOR CHANNELS A & B

Start

Bit

Stop

Bit

RX

S

S

S

S

T

D0:D7

D0:D7

D0:D7

T

D0:D7

TSSI

D0:D7

S

T

S

D0:D7

T

D0:D7

T

RX FIFO drops

below RX

Trigger Level

INT

RX FIFO fills up to RX

Trigger Level or RX Data

Timeout

TSSR

FIFO

Empties

RXRDY#

TRRI

TRR

IOR#

(Reading data out

of RX FIFO)

RXFIFODMA

41

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]