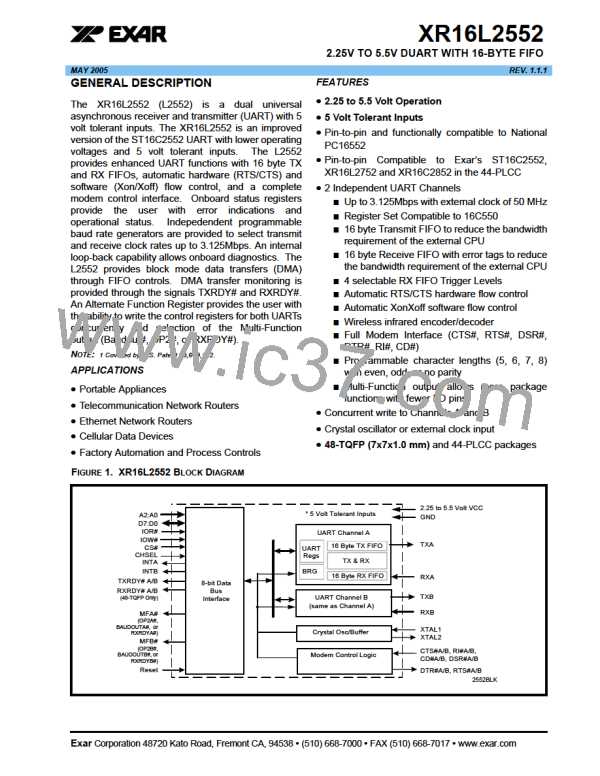

XR16L2552

2.25V TO 5.5V DUART WITH 16-BYTE FIFO

xr

REV.1.1.1

TABLE OF CONTENTS

GENERAL DESCRIPTION .................................................................................................1

APPLICATIONS................................................................................................................................................1

FEATURES .....................................................................................................................................................1

FIGURE 1. XR16L2552 BLOCK DIAGRAM ......................................................................................................................................... 1

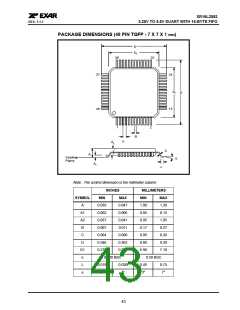

FIGURE 2. PIN OUT ASSIGNMENTS ................................................................................................................................................... 2

ORDERING INFORMATION.................................................................................................................................2

PIN DESCRIPTIONS .........................................................................................................3

1.0 PRODUCT DESCRIPTION .....................................................................................................................6

2.0 FUNCTIONAL DESCRIPTIONS .............................................................................................................7

2.1 CPU INTERFACE .............................................................................................................................................. 7

FIGURE 3. XR16L2552 DATA BUS INTERCONNECTIONS.................................................................................................................. 7

2.2 5-VOLT TOLERANT INPUTS ........................................................................................................................... 7

2.3 DEVICE RESET ................................................................................................................................................ 7

2.4 DEVICE IDENTIFICATION AND REVISION ..................................................................................................... 7

2.5 CHANNEL A AND B SELECTION .................................................................................................................... 8

TABLE 1: CHANNEL A AND B SELECT ............................................................................................................................................... 8

2.6 CHANNEL A AND B INTERNAL REGISTERS ................................................................................................ 8

2.7 SIMULTANEOUS WRITE TO CHANNEL A AND B ......................................................................................... 8

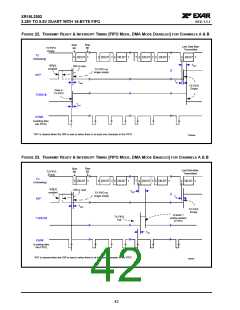

2.8 DMA MODE ....................................................................................................................................................... 8

TABLE 2: TXRDY# AND RXRDY# OUTPUTS IN FIFO AND DMA MODE............................................................................................. 9

2.9 INTA AND INTB OUPUTS ................................................................................................................................ 9

TABLE 3: INTA AND INTB PINS OPERATION FOR TRANSMITTER ........................................................................................................ 9

TABLE 4: INTA AND INTB PIN OPERATION FOR RECEIVER ............................................................................................................... 9

2.10 CRYSTAL OSCILLATOR OR EXTERNAL CLOCK INPUT ........................................................................... 9

FIGURE 4. TYPICAL OSCILLATOR CONNECTIONS............................................................................................................................... 10

2.11 PROGRAMMABLE BAUD RATE GENERATOR ......................................................................................... 10

FIGURE 5. EXTERNAL CLOCK CONNECTION FOR EXTENDED DATA RATE .......................................................................................... 10

FIGURE 6. OPERATING FREQUENCY CHART. REQUIRES A 2K OHMS PULL-UP RESISTOR ON XTAL2 PIN TO INCREASE OPERATING SPEED

11

TABLE 5: TYPICAL DATA RATES WITH A 14.7456 MHZ CRYSTAL OR EXTERNAL CLOCK ...................................................................... 11

2.12 TRANSMITTER ............................................................................................................................................. 12

2.12.1 TRANSMIT HOLDING REGISTER (THR) - WRITE ONLY....................................................................................... 12

2.12.2 TRANSMITTER OPERATION IN NON-FIFO MODE................................................................................................ 12

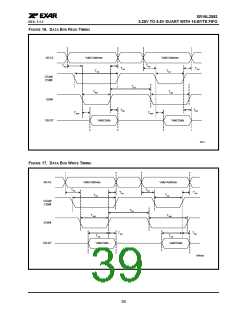

FIGURE 7. TRANSMITTER OPERATION IN NON-FIFO MODE .............................................................................................................. 12

2.12.3 TRANSMITTER OPERATION IN FIFO MODE ......................................................................................................... 12

FIGURE 8. TRANSMITTER OPERATION IN FIFO AND FLOW CONTROL MODE ..................................................................................... 13

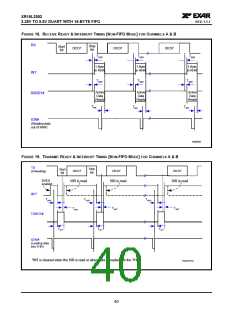

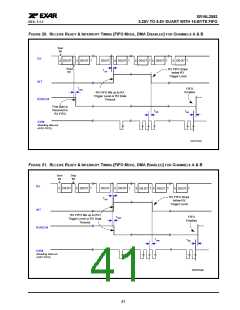

2.13 RECEIVER .................................................................................................................................................... 13

2.13.1 RECEIVE HOLDING REGISTER (RHR) - READ-ONLY .......................................................................................... 13

FIGURE 9. RECEIVER OPERATION IN NON-FIFO MODE.................................................................................................................... 14

FIGURE 10. RECEIVER OPERATION IN FIFO AND AUTO RTS FLOW CONTROL MODE ....................................................................... 14

2.14 AUTO RTS (HARDWARE) FLOW CONTROL ............................................................................................. 15

2.15 AUTO CTS FLOW CONTROL ..................................................................................................................... 15

FIGURE 11. AUTO RTS AND CTS FLOW CONTROL OPERATION....................................................................................................... 16

2.16 AUTO XON/XOFF (SOFTWARE) FLOW CONTROL ................................................................................... 17

TABLE 6: AUTO XON/XOFF (SOFTWARE) FLOW CONTROL ............................................................................................................... 17

2.17 SPECIAL CHARACTER DETECT ............................................................................................................... 17

2.18 INFRARED MODE ........................................................................................................................................ 18

FIGURE 12. INFRARED TRANSMIT DATA ENCODING AND RECEIVE DATA DECODING.......................................................................... 18

2.19 SLEEP MODE WITH AUTO WAKE-UP ....................................................................................................... 19

2.20 INTERNAL LOOPBACK .............................................................................................................................. 20

FIGURE 13. INTERNAL LOOP BACK IN CHANNEL A AND B ................................................................................................................ 20

3.0 UART INTERNAL REGISTERS ...........................................................................................................21

TABLE 7: UART CHANNEL A AND B UART INTERNAL REGISTERS...................................................................................... 21

TABLE 8: INTERNAL REGISTERS DESCRIPTION. SHADED BITS ARE ENABLED WHEN EFR BIT-4=1......................................... 22

4.0 INTERNAL REGISTER DESCRIPTIONS .............................................................................................23

4.1 RECEIVE HOLDING REGISTER (RHR) - READ- ONLY ............................................................................... 23

4.2 TRANSMIT HOLDING REGISTER (THR) - WRITE-ONLY ............................................................................ 23

4.3 BAUD RATE GENERATOR DIVISORS (DLL AND DLM) - READ/WRITE ................................................... 23

4.4 INTERRUPT ENABLE REGISTER (IER) - READ/WRITE .............................................................................. 23

I

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]