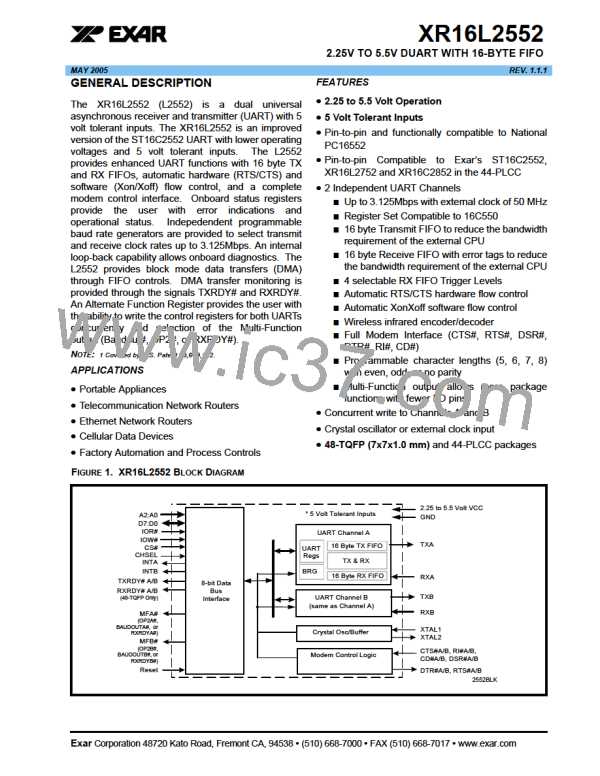

XR16L2552

2.25V TO 5.5V DUART WITH 16-BYTE FIFO

xr

REV. 1.1.1

LSR[1]: Receiver Overrun Flag

• Logic 0 = No overrun error (default).

• Logic 1 = Overrun error. A data overrun error condition occurred in the receive shift register. This happens

when additional data arrives while the FIFO is full. In this case the previous data in the receive shift register

is overwritten. Note that under this condition the data byte in the receive shift register is not transferred into

the FIFO, therefore the data in the FIFO is not corrupted by the error.

LSR[2]: Receive Data Parity Error Tag

• Logic 0 = No parity error (default).

• Logic 1 = Parity error. The receive character in RHR does not have correct parity information and is suspect.

This error is associated with the character available for reading in RHR.

LSR[3]: Receive Data Framing Error Tag

• Logic 0 = No framing error (default).

• Logic 1 = Framing error. The receive character did not have a valid stop bit(s). This error is associated with

the character available for reading in RHR.

LSR[4]: Receive Break Tag

• Logic 0 = No break condition (default).

• Logic 1 = The receiver received a break signal (RX was a logic 0 for at least one character frame time). In the

FIFO mode, only one break character is loaded into the FIFO. The break indication remains until the RX

input returns to the idle condition, “mark” or logic 1.

LSR[5]: Transmit Holding Register Empty Flag

This bit is the Transmit Holding Register Empty indicator. This bit indicates that the transmitter is ready to

accept a new character for transmission. In addition, this bit causes the UART to issue an interrupt to the host

when the THR interrupt enable is set. The THR bit is set to a logic 1 when the last data byte is transferred from

the transmit holding register to the transmit shift register. The bit is reset to logic 0 concurrently with the data

loading to the transmit holding register by the host. In the FIFO mode this bit is set when the transmit FIFO is

empty, it is cleared when the transmit FIFO contains at least 1 byte.

LSR[6]: THR and TSR Empty Flag

This bit is set to a logic 1 whenever the transmitter goes idle. It is set to logic 0 whenever either the THR or

TSR contains a data character. In the FIFO mode this bit is set to a logic 1 whenever the transmit FIFO and

transmit shift register are both empty.

LSR[7]: Receive FIFO Data Error Flag

• Logic 0 = No FIFO error (default).

• Logic 1 = A global indicator for the sum of all error bits in the RX FIFO. At least one parity error, framing error

or break indication is in the FIFO data. This bit clears when there is no more error(s) in the FIFO.

4.10 Modem Status Register (MSR) - Read Only

This register provides the current state of the modem interface signals, or other peripheral device that the

UART is connected. Lower four bits of this register are used to indicate the changed information. These bits

are set to a logic 1 whenever a signal from the modem changes state. These bits may be used as general

purpose inputs/outputs when they are not used with modem signals.

MSR[0]: Delta CTS# Input Flag

• Logic 0 = No change on CTS# input (default).

• Logic 1 = The CTS# input has changed state since the last time it was monitored. A modem status interrupt

will be generated if MSR interrupt is enabled (IER bit-3).

30

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]