xr

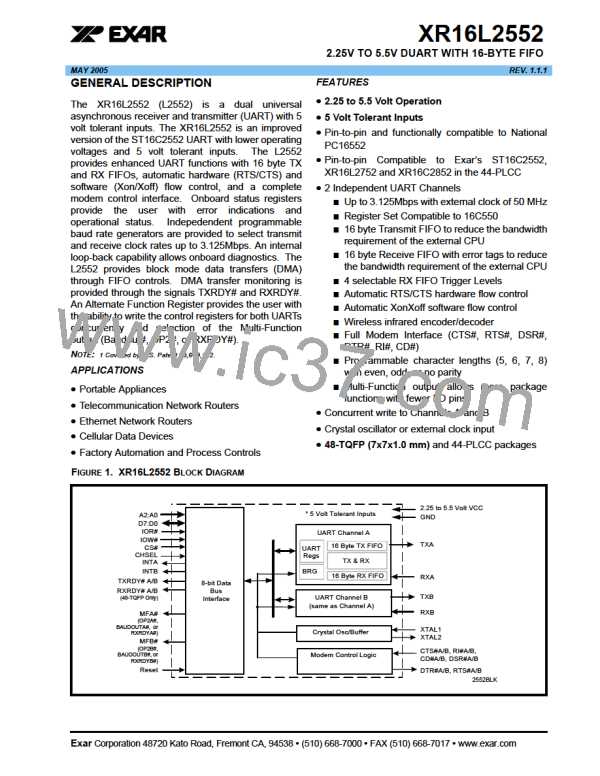

XR16L2552

2.25V TO 5.5V DUART WITH 16-BYTE FIFO

REV. 1.1.1

FCR[2]: TX FIFO Reset

This bit is only active when FCR bit-0 is a ‘1’.

• Logic 0 = No transmit FIFO reset (default).

• Logic 1 = Reset the transmit FIFO pointers and FIFO level counter logic (the transmit shift register is not

cleared or altered). This bit will return to a logic 0 after resetting the FIFO.

FCR[3]: DMA Mode Select

Controls the behavior of the TXRDY# and RXRDY# pins. See DMA operation section for details.

• Logic 0 = Normal Operation (default).

• Logic 1 = DMA Mode.

FCR[5:4]: Reserved

FCR[7:6]: Receive FIFO Trigger Select

(logic 0 = default, RX trigger level =1)

These 2 bits are used to set the trigger level for the receive FIFO. The UART will issue a receive interrupt when

the number of the characters in the FIFO crosses the trigger level. Table 10 shows the complete selections.

TABLE 10: RECEIVE FIFO TRIGGER LEVEL SELECTION

FCR

BIT-7

FCR

RECEIVE

COMPATIBILITY

BIT-6 TRIGGER LEVEL

0

0

1

1

0

1

0

1

1 (default)

Table-A. 16C550,

16C2550, 16C2552,

16C554, 16C580 com-

patible.

4

8

14

4.7

Line Control Register (LCR) - Read/Write

The Line Control Register is used to specify the asynchronous data communication format. The word or

character length, the number of stop bits, and the parity are selected by writing the appropriate bits in this

register.

LCR[1:0]: TX and RX Word Length Select

These two bits specify the word length to be transmitted or received.

BIT-1

BIT-0

WORD LENGTH

0

0

1

1

0

1

0

1

5 (default)

6

7

8

LCR[2]: TX and RX Stop-bit Length Select

The length of stop bit is specified by this bit in conjunction with the programmed word length.

STOP BIT LENGTH

(BIT TIME(S))

WORD

LENGTH

BIT-2

0

1

1

5,6,7,8

5

1 (default)

1-1/2

2

6,7,8

27

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]