áç

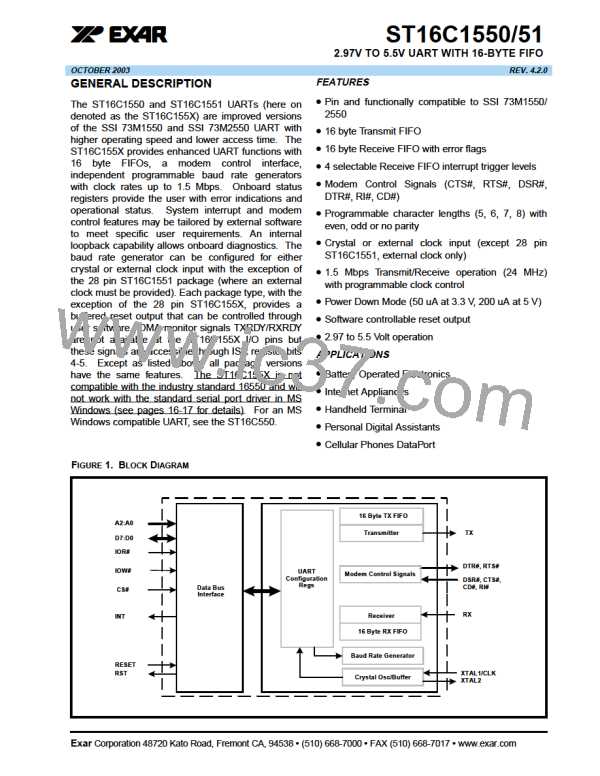

ST16C1550/51

2.97V TO 5.5V UART WITH 16-BYTE FIFO

REV. 4.2.0

• Logic 1 = A global indicator for the sum of all error bits in the RX FIFO. At least one parity error, framing error

or break indication is in the FIFO data. This bit clears when there is no more error(s) in any of the bytes in the

RX FIFO.

4.9

Modem Status Register (MSR) - Read Only

This register provides the current state of the modem interface input signals. Lower four bits of this register are

used to indicate the changed information. These bits are set to a logic 1 whenever a signal from the modem

changes state. These bits may be used for general purpose inputs when they are not used with modem

signals.

MSR[0]: Delta CTS# Input Flag

• Logic 0 = No change on CTS# input (default).

• Logic 1 = The CTS# input has changed state since the last time it was monitored. A modem status interrupt

will be generated if MSR interrupt is enabled (IER bit-3).

MSR[1]: Delta DSR# Input Flag

• Logic 0 = No change on DSR# input (default).

• Logic 1 = The DSR# input has changed state since the last time it was monitored. A modem status interrupt

will be generated if MSR interrupt is enabled (IER bit-3).

MSR[2]: Delta RI# Input Flag

• Logic 0 = No change on RI# input (default).

• Logic 1 = The RI# input has changed from a logic 0 to a logic 1, ending of the ringing signal. A modem status

interrupt will be generated if MSR interrupt is enabled (IER bit-3).

MSR[3]: Delta CD# Input Flag

• Logic 0 = No change on CD# input (default).

• Logic 1 = Indicates that the CD# input has changed state since the last time it was monitored. A modem

status interrupt will be generated if MSR interrupt is enabled (IER bit-3).

MSR[4]: CTS Input Status

CTS# (active high, logical 1). Normally this bit is the compliment of the CTS# input. In the loopback mode, this

bit is equivalent to bit-1 in the MCR register. The CTS# input may be used as a general purpose input when the

modem interface is not used.

MSR[5]: DSR Input Status

DSR# (active high, logical 1). Normally this bit is the compliment of the DSR# input. In the loopback mode, this

bit is equivalent to bit-0 in the MCR register. The DSR# input may be used as a general purpose input when the

modem interface is not used.

MSR[6]: RI Input Status

RI# (active high, logical 1). Normally this bit is the compliment of the RI# input. In the loopback mode this bit is

equivalent to bit-2 in the MCR register. The RI# input may be used as a general purpose input when the

modem interface is not used.

MSR[7]: CD Input Status

CD# (active high, logical 1). Normally this bit is the compliment of the CD# input. In the loopback mode this bit

is equivalent to bit-3 in the MCR register. The CD# input may be used as a general purpose input when the

modem interface is not used.

4.10 Scratch Pad Register (SPR) - Read/Write

This is a 8-bit general purpose register for the user to store temporary data. The content of this register is

preserved during sleep mode but becomes 0xFF (default) after a reset or a power off-on cycle.

23

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]