4 APPLICATIONS

4.1 Overview

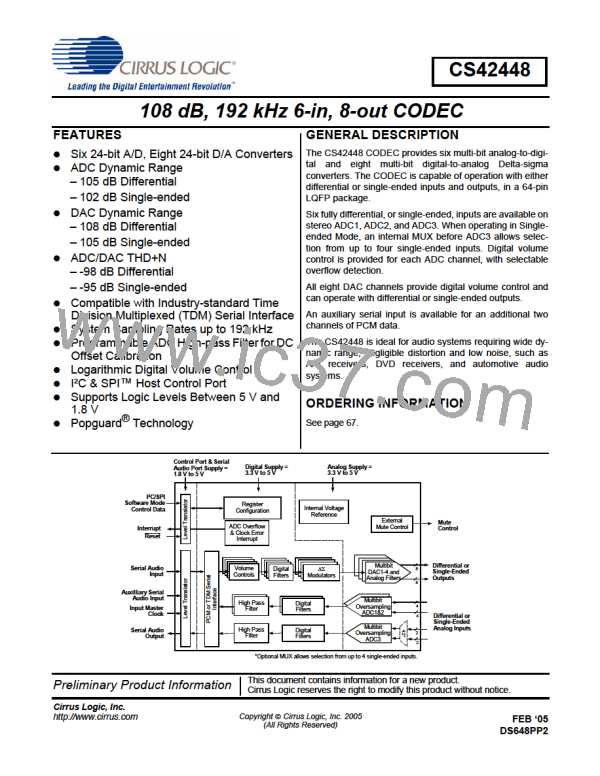

The CS42448 is a highly integrated mixed signal 24-bit audio CODEC comprised of 6 analog-to-digital

converters (ADC), implemented using multi-bit delta-sigma techniques, and 8 digital-to-analog converters

(DAC) also implemented using multi-bit delta-sigma techniques.

Other functions integrated within the CODEC include independent digital volume controls for each DAC,

digital de-emphasis filters for the DAC, digital volume control with gain on each ADC channel, ADC high-

pass filters, an on-chip voltage reference and Popguard® technology that minimizes the effects of output

transients on power-up and power-down.

All serial data is transmitted through two independent serial ports: the DAC serial port and the ADC serial

port. Each serial port can be configured independently to operate at different sample and clock rates, but

both must run synchronous to each other.

The serial audio interface ports allow up to 8 DAC channels and 8 ADC channels in a Time-Division Mul-

tiplexed (TDM) interface format. In the One-Line Mode (OLM) interface format, the CS42448 will allow up

to 6 ADC channels on one data line and up to 8 DAC channels on 2 data lines.

The CS42448 features an Auxiliary Port used to accommodate an additional two channels of PCM data

on the ADC_SDOUT data line in the TDM digital interface format. See “AUX Port Digital Interface For-

mats” on page 37 for details.

The CS42448 operates in one of three oversampling modes based on the input sample rate. When oper-

ating the CODEC as a slave, mode selection is determined automatically based on the MCLK frequency

setting. When operating as a master, mode selection is determined by the ADC and DAC FM bits in reg-

ister “Functional Mode (address 03h)” on page 46. Single-Speed mode (SSM) supports input sample

rates up to 50 kHz and uses a 128x oversampling ratio. Double-Speed mode (DSM) supports input sam-

ple rates up to 100 kHz and uses an oversampling ratio of 64x. Quad-Speed mode (QSM) supports input

sample rates up to 200 kHz and uses an oversampling ratio of 32x (NOTE: QSM for the ADC is only sup-

ported in the I²S, Left-Justified, Right-Justified interface formats. QSM for the DAC is supported in the I²S,

Left-Justified, Right-Justified and Time Division Multiplexed interface formats).

All functions can be configured through software via a serial control port operable in SPI mode or in I²C

mode.

Figure 1 on page 10 shows the recommended connections for the CS42448. See section “Register De-

scription” on page 44 for the default register settings and options.

4.2

Analog Inputs

4.2.1 Line Level Inputs

AINx+ and AINx- are the line level differential analog inputs internally biased to VQ, approxi-

mately VA/2. Figure 10 on page 27 shows the full-scale analog input levels. The CS42448 also

accommodates single-ended signals on all inputs, AIN1-AIN6. See “ADC Input Filter” on

page 56 for the recommended input filters.

For single-ended operation on ADC1-ADC3 (AIN1 to AIN6), the ADCx_SINGLE bit in the regis-

ter “ADC Control & DAC De-emphasis (address 05h)” on page 49 must be set appropriately (see

Figure 27 on page 56 for required external components).

The gain/attenuation of the signal can be adjusted for each AINx independently through the

“AINX Volume Control (address 11h-16h)” on page 53.

26

DS648PP2

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]