BSI

BS62UV1024

(1,6)

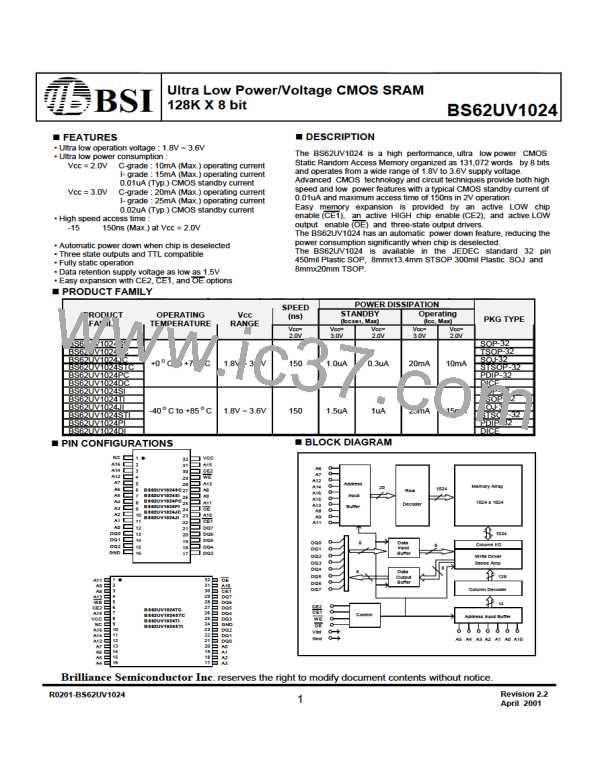

WRITE CYCLE2

t

WC

ADDRESS

(11)

CW

t

(5)

(5)

CE1

(11)

CW

CE2

t

t

WR2

t

AW

(3)

t

WP

(2)

t

DH

WE

t

AS

(4,10)

(7)

(8)

t

WHZ

D OUT

t

DW

(8,9)

t

DH

D IN

NOTES:

1. WE must be high during address transitions.

2. The internal write time of the memory is defined by the overlap of CE1 and CE2 active and WE low.

All signals must be active to initiate a write and any one signal can terminate a write by going

inactive. The data input setup and hold timing should be referenced to the second transition edge

of the signal that terminates the write.

3. TWR is measured from the earlier of CE1 or WE going high or CE2 going low at the end of write

cycle.

4. During this period, DQ pins are in the output state so that the input signals of opposite phase to the

outputs must not be applied.

5. If the CE1 low transition or the CE2 high transition occurs simultaneously with the WE low

transitions or after the WE transition, output remain in a high impedance state.

6. OE is continuously low (OE = VIL ).

7. DOUT is the same phase of write data of this write cycle.

8. DOUT is the read data of next address.

9. If CE1 is low and CE2 is high during this period, DQ pins are in the output state. Then the data input

signals of opposite phase to the outputs must not be applied to them.

10. Transition is measured 500mV from steady state with CL = 5pF as shown in Figure 1B. The

parameter is guaranteed but not 100% tested.

11. TCW is measured from the later of CE1 going low or CE2 going high to the end of write.

Revision 2.2

April 2001

R0201-BS62UV1024

7

BSI [ BRILLIANCE SEMICONDUCTOR ]

BSI [ BRILLIANCE SEMICONDUCTOR ]