TSC2005

www.ti.com

SBAS379–DECEMBER 2006

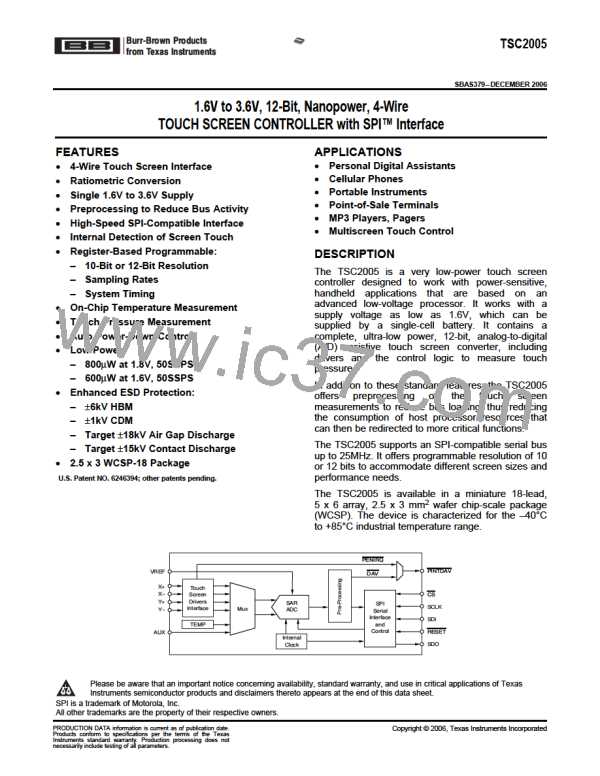

PIN CONFIGURATION

YZL PACKAGE

WCSP-18

(TOP VIEW, SOLDER BUMPS ON BOTTOM SIDE)

AGND

VREF SNSVDD

X+

NC

Y+

SUBGND

5

4

3

2

1

AUX

NC

NC

NC

X-

I/OVDD

DGND

NC

NC

Y-

NC

NC

NC

NC

SNSGND

SDI

SCLK

SDO

RESET PINTDAV

CS

F

A

B

C

D

E

Columns

(FRONT VIEW)

PIN ASSIGNMENTS

PIN

NO.

NAME

I/O

A/D DESCRIPTION

A1

A2

A3

A4

A5

B1

RESET

DGND

I

D

System reset. All register values reset to default value.

Digital ground

I/OVDD

AUX

Digital I/O interface voltage

Auxiliary channel input

I

A

D

AGND

Analog ground

PINTDAV

O

Interrupt output. Data available or PENIRQ depends on setting. Pin polarity with active low.

B2, B3,

B4, C2,

D2, E2,

E3, E4

NC

No connection.

B5

C1

VREF

SDI

I

I

A

D

External reference input

Serial data input. This input is the MOSI signal for the SPI interface protocol.

C3, C4,

D3, D4

NC

No connection. Sensitive area; avoid trace beneath. Some bumps on the WCSP may be depopulated.

C5

D1

D5

E1

E5

F1

F2

F3

F4

F5

SNSVDD

SCLK

X+

Power supply for sensor drivers and other analog blocks.

I

I

D

A

D

A

D

Serial clock input

X+ channel input

SDO

O

I

Serial data output. This output is the MISO for the SPI interface protocol.

Y+

Y+ channel input

CS

I

Chip select. This input is the slave select (SS) signal for the SPI interface protocol.

SNSGND

Y–

Sensor driver return

I

I

A

A

Y– channel input

X–

X– channel input

SUBGND

Substrate ground (for ESD current)

5

Submit Documentation Feedback

BB [ BURR-BROWN CORPORATION ]

BB [ BURR-BROWN CORPORATION ]