PCM3793A

PCM3794A

www.ti.com

SLAS529A–JANUARY 2007–REVISED FEBRUARY 2007

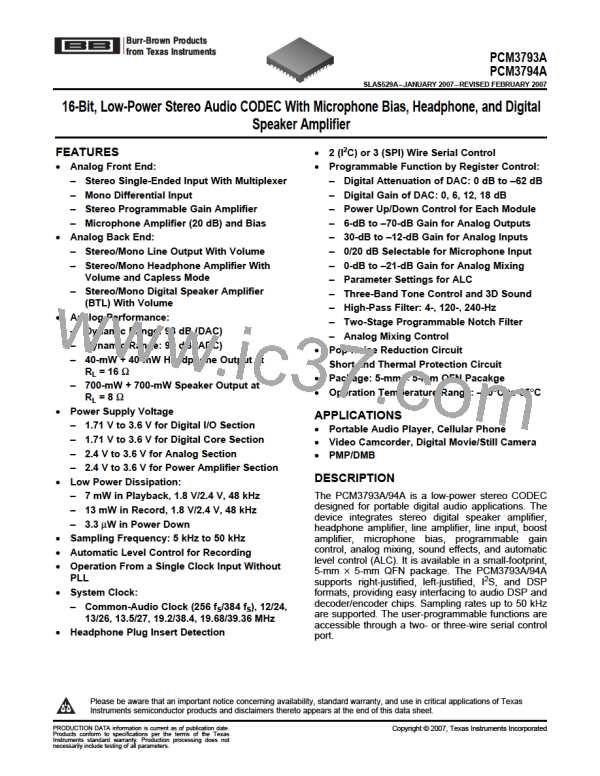

Packet Protocol

The master device must control packet protocol, which consists of start condition, slave address with read/write

bit, data (if write) or acknowledgement (if read), and stop condition. The PCM3793A/94A supports only slave

receiver and slave transmitter.

SDA

SCL

St

1−7

8

9

1−8

9

1−8

9

Sp

Slave Address R/W

ACK

DATA

ACK

DATA

ACK

R/W: Read Operation if 1; Otherwise, Write Operation

ACK: Acknowledgement of a Byte if 0

DATA: 8 Bits (Byte)

Start

Condition

Stop

Condition

Write Operation

Transmitter

Data Type

M

M

M

S

M

S

M

S

M

St

Slave Address

R/W

ACK

DATA

ACK

DATA

ACK

Sp

Read Operation

Transmitter

Data Type

M

M

M

S

S

M

S

M

M

St

Slave Address

R/W

ACK

DATA

ACK

DATA

NACK

Sp

M: Master Device

St: Start Condition

S: Slave Device

Sp: Stop Condition

T0049-03

Figure 33. Basic I2C Framework

WRITE OPERATION

The master can write any PCM3793A/94A registers in a single access. The master sends a PCM3793A/94A

slave address with a write bit, a register address, and data. When undefined registers are accessed, the

PCM3793A/94A does not send any acknowledgement. Figure 34 shows a diagram of the write operation.

Transmitter

Data Type

M

M

M

S

M

S

M

S

M

St

Slave Address

W

ACK

Reg Address

ACK

Write Data

ACK

Sp

M: Master Device S: Slave Device

St: Start Condition W: Write ACK: Acknowledge Sp: Stop Condition

R0002-01

Figure 34. Framework for Write Operation

READ OPERATION

The master can read PCM3793A/94A register. The value of the register address is stored in an indirect index

register in advance. The master sends a PCM3793A/94A slave address with a read bit after storing the register

address. Then the PCM3793A/94A transfers the data which the index register specifies. Figure 35 shows a

diagram of the read operation.

29

Submit Documentation Feedback

BB [ BURR-BROWN CORPORATION ]

BB [ BURR-BROWN CORPORATION ]