Table 14-6. Output Clock versus Selection and Prescaler

PCLKSELn

PPREn1

PPREn0

CLKPSCn output

CLK I/O

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

CLK I/O / 4

CLK I/O / 32

CLK I/O / 256

CLK PLL

CLK PLL / 4

CLK PLL / 32

CLK PLL / 256

14.15 Interrupts

This section describes the specifics of the interrupt handling as performed in

ATmega16/32/64/M1/C1.

14.15.1 Interrupt Vector

PSC provides 2 interrupt vectors:

• PSC_End (End of Cycle): When enabled and when a match with POCR_RB occurs

• PSC_Fault (Fault Event): When enabled and when a PSC input detects a Fault event.

14.15.2 PSC Interrupt Vectors in ATmega16/32/64/M1/C1

Table 14-7. PSC Interrupt Vectors

Vector

No.

Program

Address

Source

Interrupt Definition

-

5

6

-

-

-

-

0x0004

PSC_Fault

PSC Fault event

0x0005

PSC_End

PSC End of Cycle

-

-

-

-

-

-

-

150

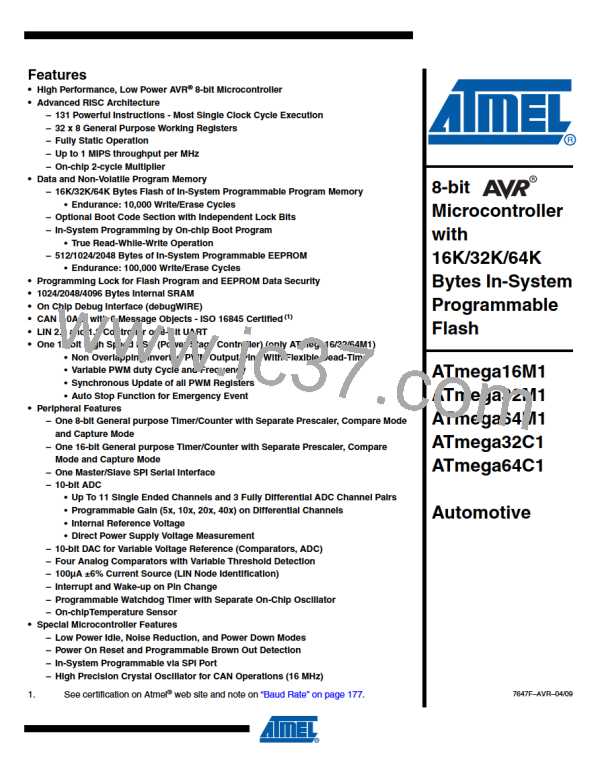

ATmega16/32/64/M1/C1

7647F–AVR–04/09

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]