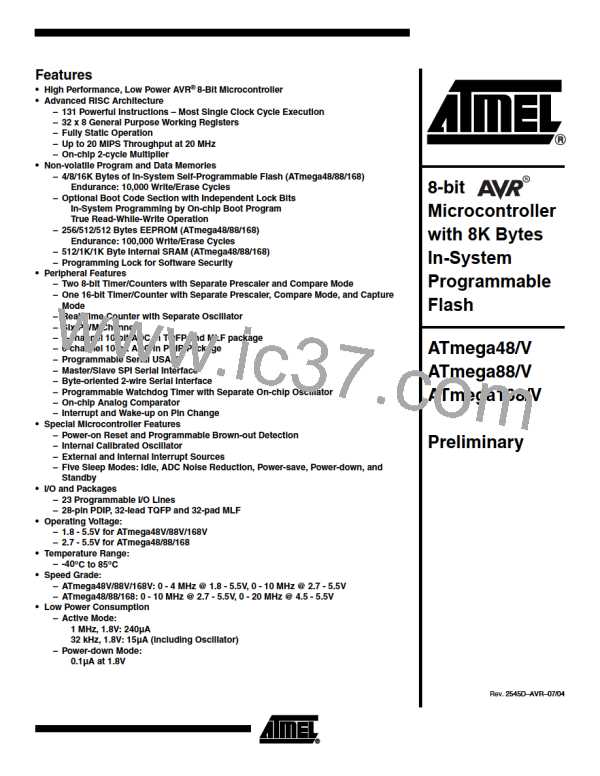

ATmega48/88/168

After a repeated START condition (state 0x10) the 2-wire Serial Interface can access

the same Slave again, or a new Slave without transmitting a STOP condition. Repeated

START enables the Master to switch between Slaves, Master Transmitter mode and

Master Receiver mode without losing control of the bus.

Table 91. Status codes for Master Transmitter Mode

Status Code

(TWSR)

Prescaler Bits

are 0

Application Software Response

To/from TWDR To TWCR

STO TWINT

Status of the 2-wire Serial Bus

and 2-wire Serial Interface Hard-

ware

STA

0

TWEA

X

Next Action Taken by TWI Hardware

0x08

A START condition has been Load SLA+W

transmitted

0

1

SLA+W will be transmitted;

ACK or NOT ACK will be received

0x10

A

repeated START condition Load SLA+W or

0

0

0

0

1

1

X

X

SLA+W will be transmitted;

ACK or NOT ACK will be received

SLA+R will be transmitted;

has been transmitted

Load SLA+R

Logic will switch to Master Receiver mode

0x18

0x20

0x28

0x30

0x38

SLA+W has been transmitted;

ACK has been received

Load data byte or

0

0

1

X

Data byte will be transmitted and ACK or NOT ACK will

be received

Repeated START will be transmitted

STOP condition will be transmitted and

TWSTO Flag will be reset

No TWDR action or

No TWDR action or

1

0

0

1

1

1

X

X

No TWDR action

Load data byte or

1

0

1

0

1

1

X

X

STOP condition followed by a START condition will be

transmitted and TWSTO Flag will be reset

SLA+W has been transmitted;

NOT ACK has been received

Data byte will be transmitted and ACK or NOT ACK will

be received

Repeated START will be transmitted

STOP condition will be transmitted and

TWSTO Flag will be reset

No TWDR action or

No TWDR action or

1

0

0

1

1

1

X

X

No TWDR action

1

0

1

0

1

1

X

X

STOP condition followed by a START condition will be

transmitted and TWSTO Flag will be reset

Data byte has been transmitted; Load data byte or

ACK has been received

Data byte will be transmitted and ACK or NOT ACK will

be received

Repeated START will be transmitted

STOP condition will be transmitted and

TWSTO Flag will be reset

No TWDR action or

No TWDR action or

1

0

0

1

1

1

X

X

No TWDR action

1

0

1

0

1

1

X

X

STOP condition followed by a START condition will be

transmitted and TWSTO Flag will be reset

Data byte has been transmitted; Load data byte or

NOT ACK has been received

No TWDR action or

Data byte will be transmitted and ACK or NOT ACK will

be received

Repeated START will be transmitted

STOP condition will be transmitted and

TWSTO Flag will be reset

1

0

0

1

1

1

X

X

No TWDR action or

No TWDR action

1

1

1

X

STOP condition followed by a START condition will be

transmitted and TWSTO Flag will be reset

Arbitration lost in SLA+W or data No TWDR action or

bytes

0

1

0

0

1

1

X

X

2-wire Serial Bus will be released and not addressed

Slave mode entered

A START condition will be transmitted when the bus be-

comes free

No TWDR action

215

2545D–AVR–07/04

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]