Table 33. Overriding Signals for Alternate Functions in PD3..PD0

Signal Name

PUOE

PUOV

DDOE

DDOV

PVOE

PVOV

DIEOE

DIEOV

DI

PD3/INT1

PD2/INT0

PD1/TXD

PD0/RXD

0

0

TXEN

RXEN

0

0

0

PORTD0 • PUD

0

0

TXEN

RXEN

0

0

1

0

0

0

TXEN

0

0

0

TXD

0

INT1 ENABLE

INT0 ENABLE

0

0

–

–

0

1

1

0

INT1 INPUT

–

INT0 INPUT

–

RXD

–

AIO

Register Description for

I/O Ports

Port A Data Register – PORTA

Bit

7

6

5

4

PORTA4

R/W

0

3

PORTA3

R/W

0

2

1

0

PORTA7

R/W

0

PORTA6

R/W

0

PORTA5

R/W

0

PORTA2

R/W

0

PORTA1

R/W

0

PORTA0

R/W

0

PORTA

Read/Write

Initial Value

Port A Data Direction Register

– DDRA

Bit

7

DDA7

R/W

0

6

DDA6

R/W

0

5

DDA5

R/W

0

4

DDA4

R/W

0

3

DDA3

R/W

0

2

DDA2

R/W

0

1

DDA1

R/W

0

0

DDA0

R/W

0

DDRA

Read/Write

Initial Value

Port A Input Pins Address –

PINA

Bit

7

PINA7

R

6

PINA6

R

5

PINA5

R

4

PINA4

R

3

PINA3

R

2

PINA2

R

1

PINA1

R

0

PINA0

R

PINA

Read/Write

Initial Value

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

Port B Data Register – PORTB

Bit

7

PORTB7

R/W

0

6

PORTB6

R/W

0

5

PORTB5

R/W

0

4

PORTB4

R/W

0

3

PORTB3

R/W

0

2

PORTB2

R/W

0

1

PORTB1

R/W

0

0

PORTB0

R/W

0

PORTB

Read/Write

Initial Value

Port B Data Direction Register

– DDRB

Bit

7

DDB7

R/W

0

6

DDB6

R/W

0

5

DDB5

R/W

0

4

DDB4

R/W

0

3

DDB3

R/W

0

2

DDB2

R/W

0

1

DDB1

R/W

0

0

DDB0

R/W

0

DDRB

Read/Write

Initial Value

62

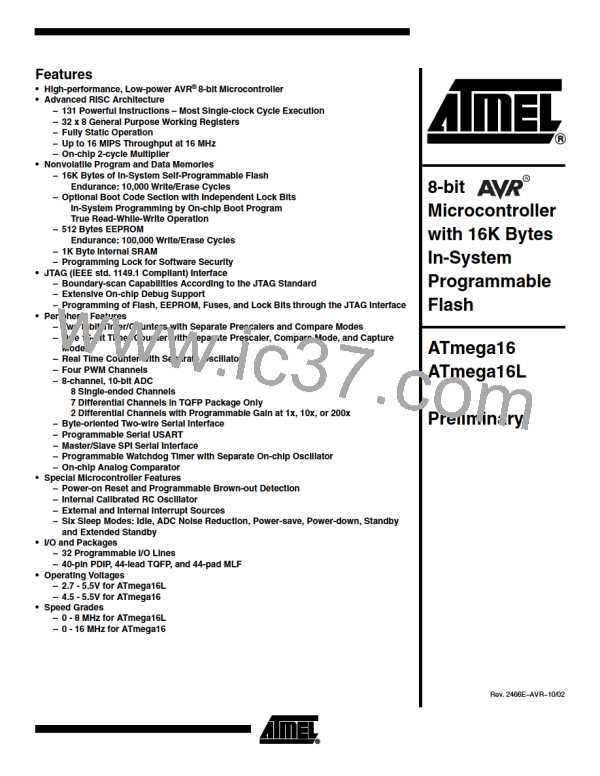

ATmega16(L)

2466E–AVR–10/02

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]