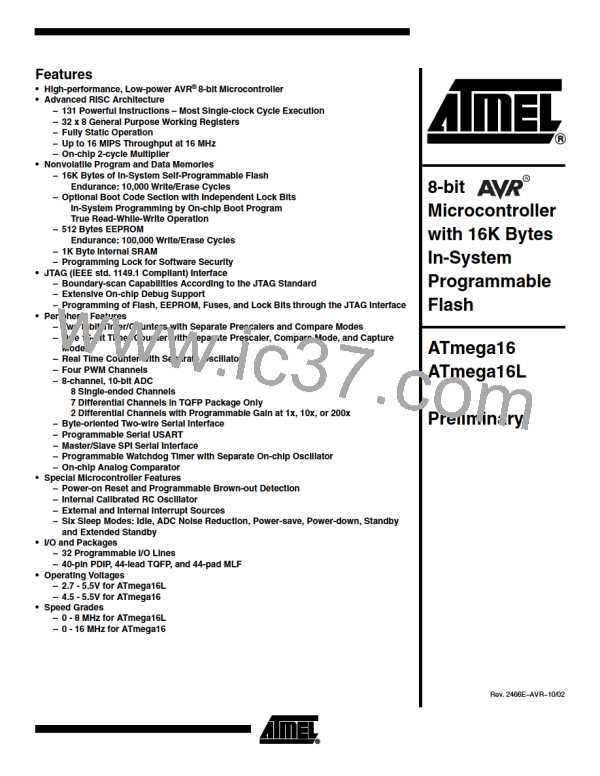

ATmega16(L)

Internal Voltage

Reference

ATmega16 features an internal bandgap reference. This reference is used for Brown-

out Detection, and it can be used as an input to the Analog Comparator or the ADC. The

2.56V reference to the ADC is generated from the internal bandgap reference.

Voltage Reference Enable

Signals and Start-up Time

The voltage reference has a start-up time that may influence the way it should be used.

The start-up time is given in Table 16. To save power, the reference is not always turned

on. The reference is on during the following situations:

1. When the BOD is enabled (by programming the BODEN Fuse).

2. When the bandgap reference is connected to the Analog Comparator (by setting

the ACBG bit in ACSR).

3. When the ADC is enabled.

Thus, when the BOD is not enabled, after setting the ACBG bit or enabling the ADC, the

user must always allow the reference to start up before the output from the Analog Com-

parator or ADC is used. To reduce power consumption in Power-down mode, the user

can avoid the three conditions above to ensure that the reference is turned off before

entering Power-down mode.

Table 16. Internal Voltage Reference Characteristics

Symbol

VBG

Parameter

Min

Typ

1.23

40

Max

1.35

70

Units

V

Bandgap reference voltage

Bandgap reference start-up time

Bandgap reference current consumption

1.15

tBG

µs

IBG

10

µA

Watchdog Timer

The Watchdog Timer is clocked from a separate On-chip Oscillator which runs at 1

MHz. This is the typical value at VCC = 5V. See characterization data for typical values at

other VCC levels. By controlling the Watchdog Timer prescaler, the Watchdog Reset

interval can be adjusted as shown in Table 17 on page 40. The WDR – Watchdog Reset

– instruction resets the Watchdog Timer. The Watchdog Timer is also reset when it is

disabled and when a Chip Reset occurs. Eight different clock cycle periods can be

selected to determine the reset period. If the reset period expires without another

Watchdog Reset, the ATmega16 resets and executes from the Reset Vector. For timing

details on the Watchdog Reset, refer to page 38.

To prevent unintentional disabling of the Watchdog, a special turn-off sequence must be

followed when the Watchdog is disabled. Refer to the description of the Watchdog Timer

Control Register for details.

Figure 21. Watchdog Timer

WATCHDOG

OSCILLATOR

39

2466E–AVR–10/02

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]