Power-on Reset

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detec-

tion level is defined in Table 15. The POR is activated whenever VCC is below the

detection level. The POR circuit can be used to trigger the Start-up Reset, as well as to

detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reach-

ing the Power-on Reset threshold voltage invokes the delay counter, which determines

how long the device is kept in RESET after VCC rise. The RESET signal is activated

again, without any delay, when VCC decreases below the detection level.

Figure 16. MCU Start-up, RESET Tied to VCC

.

VPOT

VCC

VRST

RESET

tTOUT

TIME-OUT

INTERNAL

RESET

Figure 17. MCU Start-up, RESET Extended Externally

VPOT

VCC

VRST

RESET

tTOUT

TIME-OUT

INTERNAL

RESET

External Reset

An External Reset is generated by a low level on the RESET pin. Reset pulses longer

than the minimum pulse width (see Table 15) will generate a reset, even if the clock is

not running. Shorter pulses are not guaranteed to generate a reset. When the applied

signal reaches the Reset Threshold Voltage – VRST – on its positive edge, the delay

counter starts the MCU after the Time-out period tTOUT has expired.

36

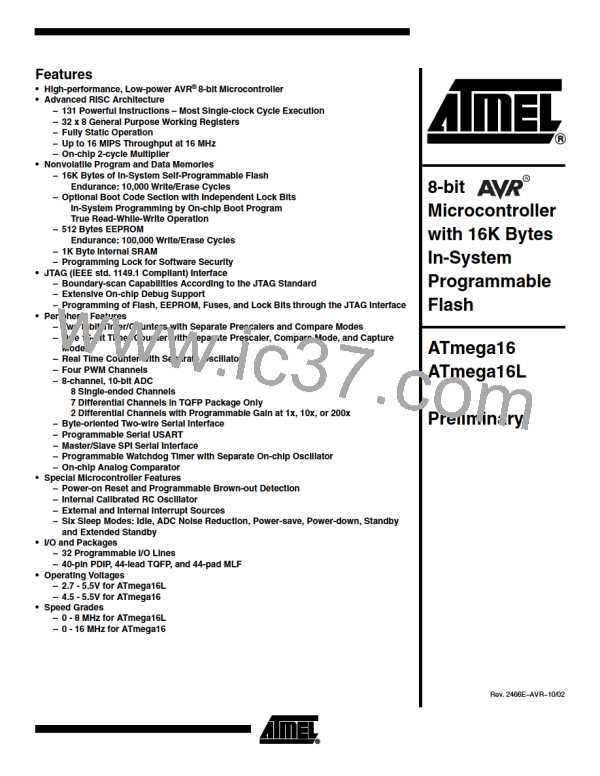

ATmega16(L)

2466E–AVR–10/02

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]