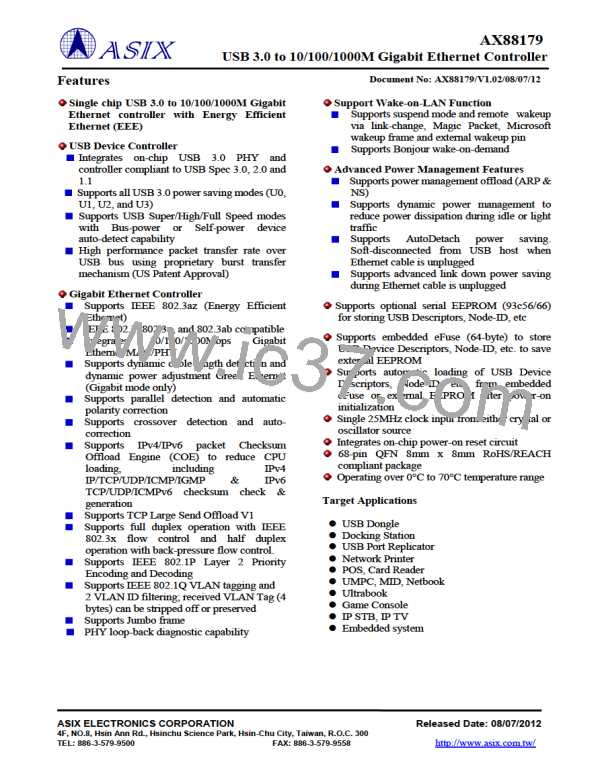

AX88179

USB 3.0 to 10/100/1000M Gigabit Ethernet Controller

6.2.2.20 COE PPPoE Control Register (CPCR, 36h, R/W)

Bit7

Bit6

Bit5

Reserved

Bit4

Bit3

Bit2

Bit1

TX

Bit0

RX

RX: L2 parser support PPPoE encapsulated packet in RX path.

0: COE doesn’t support PPPoE encapsulated packet in RX path.

1: COE support PPPoE encapsulated packet in RX path.

TX: L2 parser support PPPoE encapsulated packet in TX path.

0: COE doesn’t support PPPoE encapsulated packet in TX path.

1: COE support PPPoE encapsulated packet in TX path.

6.2.2.21 Pause Water Level HIGH Register (PWLHR, 54h)

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

Reserved

AA [7:0]

AA [6:0]: High water level for flow control. Default value is 7’h42 (R/W)

Note that unit is 128bytes.

AA [7]: Reserved

6.2.2.22 Pause Water Level LOW Register (PWLLR, 55h)

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

Reserved

AA [7:0]

AA [6:0]: Low water level for flow control. Default value is 7’h24 (R/W)

Note that unit is 128bytes.

AA [7]: Reserved

6.2.2.23 PIN Control Register (PINCR, 70h)

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

Reserved

MFA_EN

PME_PIN

PME_PIN: GPIO_0 is PME PIN. (R/W)

0: GPIO_0 operates as GPIO.

1: GPIO_0 is PME PIN (default).

MFA_EN: Enable MFA function as GPIO. (R/W)

0: MFA pins operate as LED indication (default).

1: MFA pins operate as GPIO function.

48

Copyright © 2011-2012 ASIX Electronics Corporation. All rights reserved.

ASIX [ ASIX ELECTRONICS CORPORATION ]

ASIX [ ASIX ELECTRONICS CORPORATION ]