These choices make it possible to use the macrocell as

an output, an input, a bidirectional pin, or a three-state

output for use in driving a bus.

should be programmed. The configuration file is dis-

cussed in detail in the MACHPRO software manual.

The MACH211SP devices tristate the outputs during

programming.They have one security bit which inhibits

program and verify.This allows the user to protect pro-

prietary patterns and designs.

Power-Down Mode

The MACH211SP features a programmable low-power

mode in which individual signal paths can be pro-

grammed as low power. These low-power speed paths

will be slightly slower than the non-low-power paths.

This feature allows speed critical paths to run at maxi-

mum frequency while the rest of the paths operate in

the low-power mode, resulting in power savings of up

to 75%. If all signals in a PAL block are low-power, then

total power is reduced further.

Program verification of a MACH device involves read-

ing back the programmed pattern and comparing it with

the original JEDEC file. The AMD method of program

verification performed on the MACH devices permits

the verification of one device at a time.

Accidental Programming or Erasure

Protection

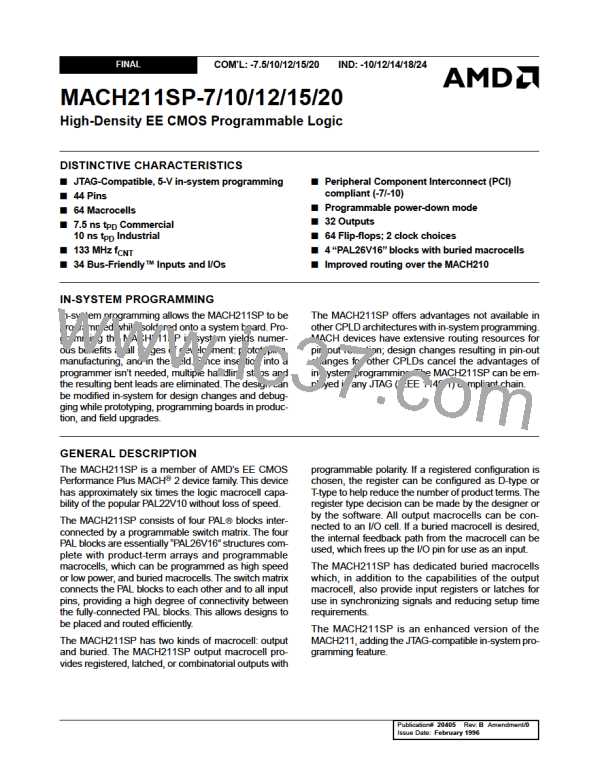

In-System Programming

It is virtually impossible to program or erase a MACH

device inadvertently. The following conditions must be

met before programming actually takes place:

Programming is the process where MACH devices are

loaded with a pattern defined in a JEDEC file obtained

from MACHXL software or third-party software. Pro-

gramming is accomplished through four JTAG pins:

Test Mode Select (TMS), Test Clock (TCK), Test Data

In (TDI), and Test Data Out (TDO). The MACH211SP

can be employed in any JTAG (IEEE 1149.1) compli-

ant chain. While the MACH211SP is fully JTAG com-

patible, it supports the BYPASS instruction, not the

EXTEST and SAMPLE/PRELOAD instructions. The

MACH211SP can be programmed across the commer-

cial temperature range. Programming the MACH de-

vice after it has been placed on a circuit board is easily

accomplished. Programming is initiated by placing the

device into programming mode, using the MACHPRO

programming software provided by AMD. The device is

bulk erased and the JEDEC file is then loaded. After

the data is transferred into the device, the PROGRAM

instruction is loaded. Further programming details can

be found in application note, “Advanced In-circuit

Programming Guidelines.”

■ The device must be in the password-protected

program mode

■ The programming or bulk erase instruction must be

in the instruction register

If the above conditions are not met, the programming

circuitry cannot be activated.

To ensure that the AMD ten year device data retention

guarantee applies, 100 program/erase cycle limit

should not be exceeded.

Bus-Friendly Inputs and I/Os

The MACH211SP inputs and I/Os include two inverters

in series which loop back to the input. This double

inversion reinforces the state of the input and pulls the

voltage away from the input threshold voltage. For an

illustration of this configuration, please turn to the

Input/Output Equivalent Schematics section.

On-Board Programming Options

PCI Compliance

Since the MACHPRO software performs these steps

automatically, the following programming options are

published for reference.

The MACH211SP-7/10 is fully compliant with the PCI

Local Bus Specification published by the PCI Special

Interest Group. The MACH211SP-7/10’s predictable

timing ensures compliance with the PCI AC specifica-

tions independent of the design. On the other hand, in

CPLD and FPGA architectures without predictable tim-

ing, PCI compliance is dependent upon routing and

product term distribution.

The configuration file, which is also known as the chain

file, defines the MACH device JTAG chain.The file con-

tains the information concerning which JEDEC file is to

be placed into which device, the state which the out-

puts should be placed, and whether the security fuses

8

MACH211SP-7/10/12/15/20

AMD [ AMD ]

AMD [ AMD ]