[ASAHI KASEI]

[AK7740ET]

7-4) Read-out during RUN phase (SO output )

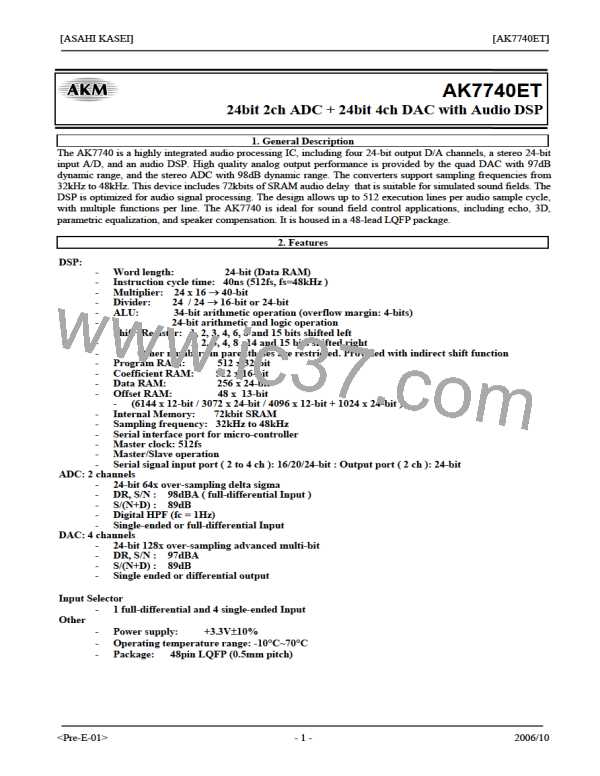

SO outputs data on DBUS (data bus) from the DSP section. Data is set when the @MICR command is executed in the

DSP program. Setting the data allows DRDY to go to "H", and data is output synchronized with the falling edge of

SCLK. When SI goes "H", DRDY goes to "L" to wait for the next command. Once DRDY goes "H", the data from

the last @MICR command immediately before DRDY went "H" is held until SI goes "H", and subsequent commands

will be rejected. A maximum of 24 bits are output from SO. After the required number of data (not exceeding 24 bits)

is taken out by SCLK, setting SI to “H” can output the next data.

S_RESET

RQ

SI

@MICR

DRDY

Data1

Data2

SCLK

SO

DM Data1

DLSB

DM Data2 DLSB

SO read (during RUN phase)

The SI pin controls clearing the output buffer (MICR). When reading this data, be aware that state changes on SI are

asynchronous to the audio sampling clock, which may result in noise in the audio sugnal.

<Pre-E-01>

- 42 -

2006/10

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]