[ASAHI KASEI]

[AK7740ET]

7-3-c) External conditional jump code rewrite (during RUN phase)

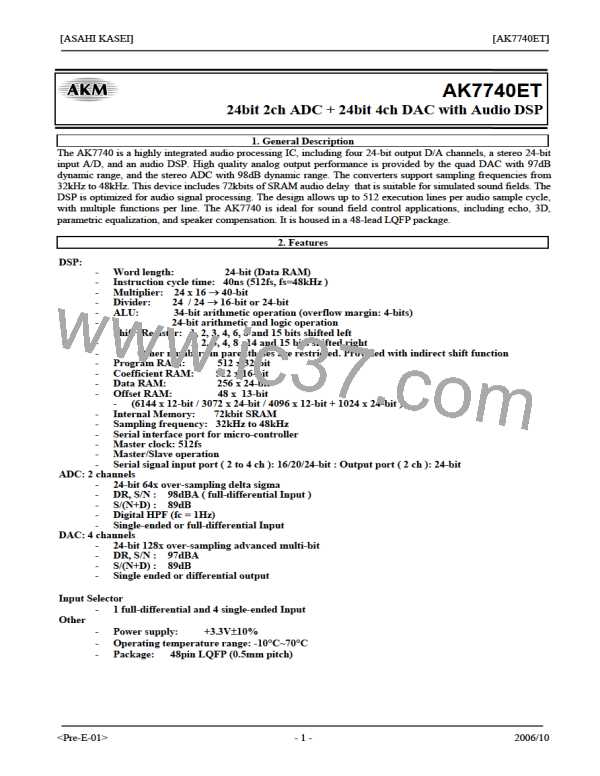

Data comprising a set of two bytes is used to write the external conditional jump code. Data can be input during both

the reset and operation phases, and input data is set to the specified register at the rising edge of LRCLK. When all

data has been transferred, the RDY terminal goes to "L". Upon completion of writing, it goes to "H". A jump

command will be executed if there is any one agreement between each bit of the 8-bit external condition code and

"1"of each bit of the IFCON field. A write operation from the microcontroller is disabled until RDY goes to "H".

Note: The LRCLK phase is inverted in the I2S-compatible mode.

Data transfer procedure

c Command code

d Code data

C4h ( 1 1 0 0 0 1 0 0 )

(D7 . . . . . D0)

max 1LRCLK

S_RESET

SCLK

SI

11000100

D7 *** D0

SO

RQ

L ch R ch

LRCLK

max 2LRCLK

RDY

max0.25LRCLK

External condition jump write timing (during RUN phase)

<Pre-E-01>

- 41 -

2006/10

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]