[ASAHI KASEI]

[AK7740ET]

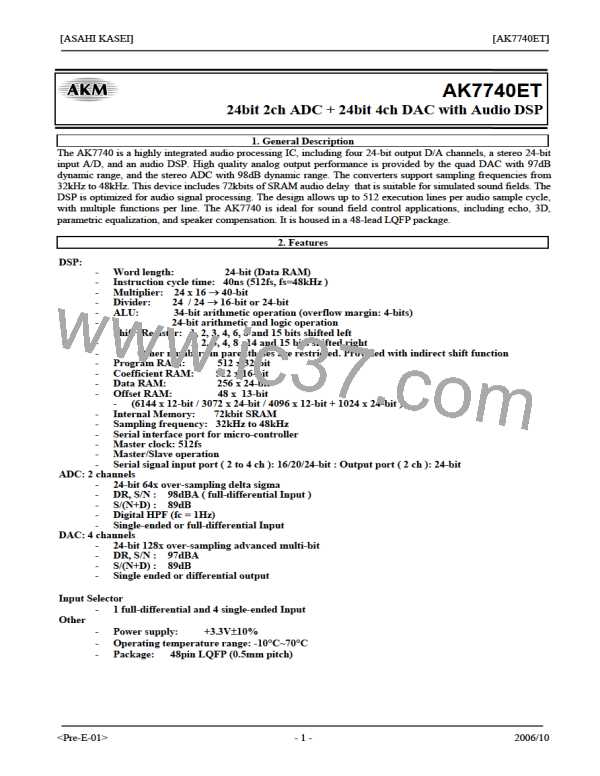

7-3) Write during RUN phase

7-3-a) CRAM rewrite preparation and write (during RUN phase)

This function is used to rewrite CRAM (coefficient RAM) during program execution. After inputting the command

code, input a maximum of 16 data bytes to rewrite to a continuous address. Then input the write command code and

rewrite the leading address. Every time the RAM address to be rewritten is specified, the contents of RAM are

rewritten. The following is an example to show how five data bytes from address "10" of the coefficient RAM are

rewritten:

Coefficient RAM execution address

7

8

9 10 11 13 16 11 12 13 14 15

È

}

È

}

È

}

È

}

È

}

Rewrite position

Ç

Note that address "13" is not executed until address "12" is rewritten.

Data transfer procedure

* Preparation for rewrite c Command code A8h ( 1 0 1 0 1 0 0 0 )

d Data

e Data

( D15 . . . . D8 )

( D7 . . . . . D0 )

* Rewrite

c Command code A4h ( 1 0 1 0 0 1 0 0 )

d Address upper

e Address lower

( 0 0 0 0 0 0 0 A8 )

(A7

.

.

.

. A0 )

S_RESET

RQ

SCLK

SI

10101000

10100100

D15 **** D0

A15 **** A0

AL

max 200ns

RDYLG

RDY

SO

Longer of (16-n) x 2 MCLK

(n: number of data) and AL

Note: The RDY signal will go to high within the maximum of two LRCLKs if the RDYLG

width is programmed to ensure a new address to be rewritten within one sampling cycle.

CRAM rewriting preparation and writing

<Pre-E-01>

- 39 -

2006/10

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]