[ASAHI KASEI]

[AK7740ET]

(5) System clock

The required system clock is XTI (384fs/512fs), LRCLK (fs) and BITCLK (64fs) in the slave mode, and it is XTI

(384 fs/512 fs) in the master mode. LRCLK corresponds to the standard digital audio rate (32 kHz, 44.1 kHz, and

48 kHz).

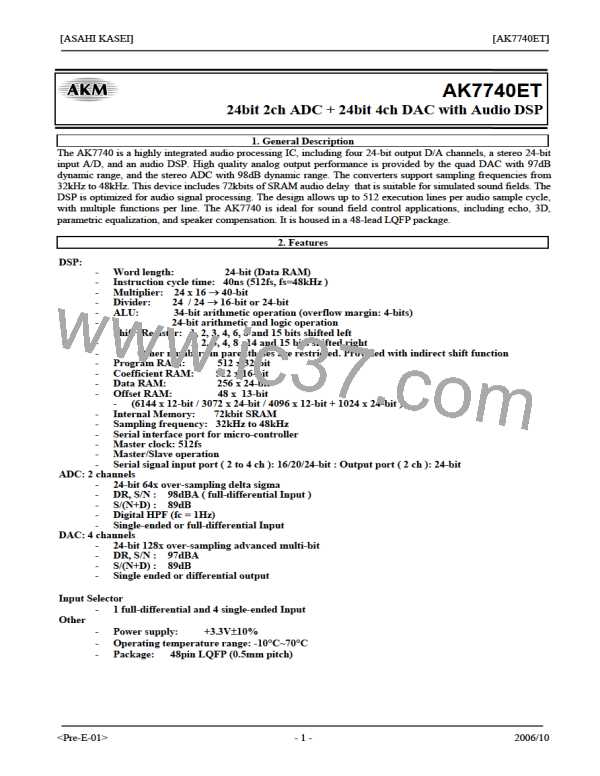

Fs

XTI(Master Clock)

BITCLK

64fs

512fs

384fs

32.0kHz

44.1kHz

48.0kHz

16.3840MHz

22.5792MHz

24.576MHz

12.2880MHz

16.9344MHz

18.4320MHz

2.0480MHz

2.8224MHz

3.0720MHz

5-1) Master clock (XTI pin)

The master clock is produced by connecting a crystal oscillator between the XTI pin and XTO pin or by inputting

an external clock into the XTI pin while the XTO pin is left open.

5-2) Slave mode

The required system clock is XTI, LRCLK (1 fs) and BITCLK (48/64fs).

The master clock (XTI) and LRCLK must be synchronized, but the phase is not critical.

5-3) Master mode

The required system clock is XTI (384fs/512fs). When the master clock (XTI) is input, LRCLK (1fs) and BITCLK

(64fs) will be outputted from the internal counter synchronized with the XTI. LRCLK and BITCLK will not be

active during initial reset ( INIT_RESET ="L") and system reset ( S_RESET ="L").

<Pre-E-01>

- 26 -

2006/10

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]