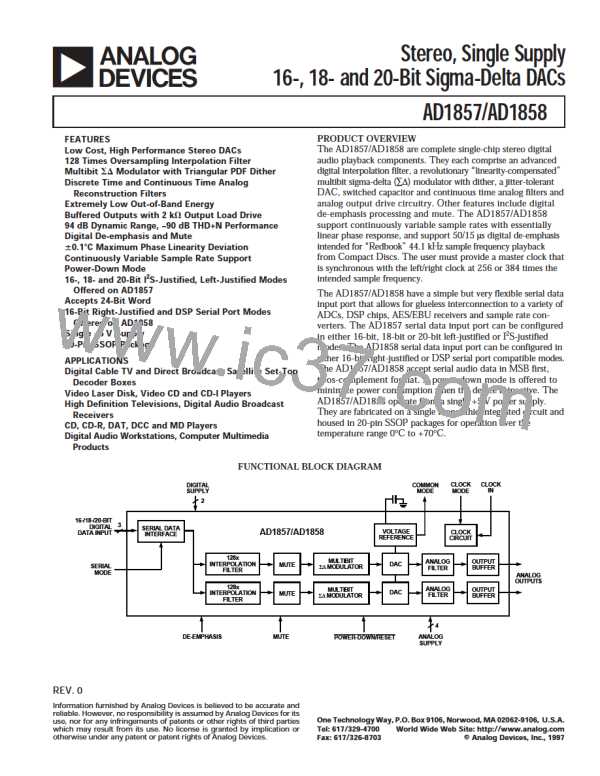

AD1857/AD1858

TH EO RY O F O P ERATIO N

T he conventional problem limiting the performance of multibit

sigma-delta converters is the nonlinearity of the passive circuit

elements used to sum the quantization levels. Analog Devices has

developed (and received patents on) a revolutionary architecture

that overcomes the circuit element linearity problem that otherwise

limits the performance of multibit sigma-delta audio converters.

T his new architecture provides the AD1857/AD1858 with the

same excellent differential nonlinearity and linearity drift (over

temperature and time) specifications as single bit sigma-delta

DACs.

T he AD1857/AD1858 offer the advantages of sigma-delta con-

version architectures (no component trims, low cost CMOS

process technology, superb low-level linearity performance) with

the advantages of conventional multibit R-2R resistive ladder

audio DACs (continuously variable sample rate support, jitter

tolerance, very low output noise, etc.).

T he use of a multibit sigma-delta modulator means that the

AD1857/AD1858 generate dramatically lower amounts of out-

of-band noise energy, which greatly reduces the requirement on

post DAC filtering. T he required post-filtering is integrated on

the AD1857/AD1858. T he AD1857/AD1858’s multibit sigma-

delta modulator is also highly immune to digital substrate noise.

T he AD1857/AD1858’s multibit modulator has another

important advantage; it has a high immunity to substrate digital

noise. Substrate noise can be a significant problem in mixed-

signal designs, where it can produce intermodulation products

that fold down into the audio band. T he AD1857/AD1858 are

approximately eight times less sensitive to digital substrate noise

(voltage reference noise injection) than equivalent single-bit

sigma-delta modulator based DACs.

Ser ial Audio D ata Inter face

T he serial audio data interface uses the bit clock (BCLK) simply

to clock the data into the AD1857/AD1858. T he bit clock may

therefore be asynchronous to the L/R clock. T he left/right clock

(LRCLK) is both a framing signal and the sample frequency

input to the interpolation filter. T he left/right clock must be

synchronous with MCLK, but may have any phase relationship

with respect to MCLK; LRCLK is generally synchronously divided

down from MCLK. T he SDAT A input carries the serial stereo

digital audio in MSB first, twos-complement format.

D ither Gener ator

T he AD1857/AD1858 include an on-chip dither generator that

is intended to further “whiten” the quantization noise introduced

by the multibit DAC. T he dither has a triangular Probability

Distribution Function (PDF) characteristic, which is generally

considered to create the most favorable noise shaping of the

residual quantization noise. The AD1857/AD1858 are among the

first low cost IC audio DACs to include dithering.

D igital Inter polation Filter

T he purpose of the interpolator is to “oversample” the input

data, i.e., to increase the sample rate so the first signal image is

moved out to the oversample frequency, which relaxes the

attenuation requirements on the analog reconstruction filter.

T he AD1857/AD1858 interpolator increases the input data

sample rate by 128. T he interpolation is performed using a

multistage FIR digital filter structure. T he first stage is a droop

equalizer; the second and third stages are halfband filters; and

the fourth stage is a second-order comb filter. T he FIR filter

implementation is multiplier-free, i.e., the multiplies are performed

using shift-and-add operations. T he FIR filter coefficients have

been recoded in a canonical sign digit format to enable the use

of a compact arithmetic logic unit without a multiplier.

Analog Filter ing

The AD1857/AD1858 include a second-order switched

capacitor discrete time low-pass filter followed by a first-order

analog continuous time low-pass filter. T hese filters eliminate

the need for any additional off-chip external reconstruction

filtering. T his on-chip switched capacitor analog filtering is

essential to reduce the deleterious effects of master clock jitter.

D igital D e-Em phasis P r ocessing

The AD1857/AD1858 include digital circuitry for implementing

the 50/15 µs de-emphasis frequency response characteristic. A

control pin DEEMP (Pin 5) enables de-emphasis when it is

asserted HI. T he digital de-emphasis response assumes a sample

frequency of 44.1 kHz. T he transfer function magnitude error

of this digital filter is less than ±0.1 dB (from 0 kHz to 20 kHz)

compared to a 50/15 µs continuous time filter. If the sample

frequency is not 44.1 kHz, the de-emphasis frequency response

will scale directly with frequency. T he 44.1 kHz FS digital de-

emphasis frequency response is shown in Figure 8.

Multibit Sigm a-D elta Modulator

T he AD1857/AD1858 employ a 4-bit second-order sigma-delta

modulator. Whereas a traditional single-bit sigma-delta

modulator has two levels of quantization, the AD1857/AD1858’s

has 17 levels of quantization. T raditional single-bit sigma-delta

modulators sample the input signal at 64 times the input sample

rate; the AD1857/AD1858 sample the input signal at 128 times

the input sample rate. T he additional quantization levels

combined with the high oversampling ratio means that the

AD1857/AD1858 DAC output spectrum contains dramatically

lower levels of out-of-band noise energy, which is a major

stumbling block with more traditional single-bit sigma-delta

architectures. This means that the post-DAC analog reconstruction

filter has reduced transition band steepness and attenuation

requirements, which directly equates to lower phase distortion.

Since the analog filtering generally establishes the noise and

distortion characteristic of the DAC, the reduced requirements

translate into better audio performance.

T1 = 50µs

0

T2 = 15µs

–10

F2

F1

10.61

3.183

FREQUENCY – kHz

Multibit sigma-delta modulators bring an additional benefit:

they are essentially free of stability (and therefore potential loop

oscillation) problems. T hey are able to scale the output signal

to a wider range of the voltage reference, which can increase the

overall dynamic range of the converter.

Figure 8. Digital De-Em phasis Frequency Response

REV. 0

–9–

ADI [ ADI ]

ADI [ ADI ]