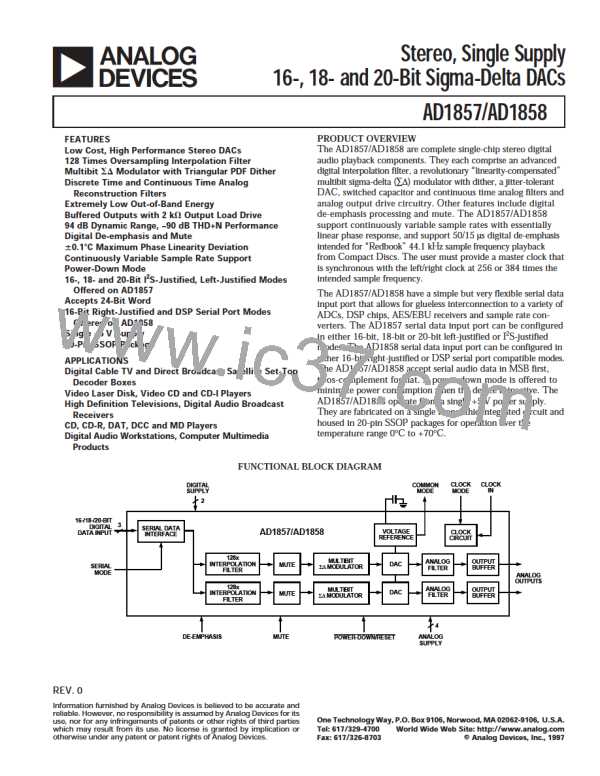

AD1857/AD1858

Contr ol Signals

Figure 18 shows the suggested interface to the Philips SAA2500*

MPEG audio decoder IC. T he SAA2500 supports 18 bits of

data using an I2S-compatible output format.

The MODE and DEEMP control inputs are normally connected

HI or LO to establish the operating state of the AD1857/AD1858.

They can be changed dynamically (and asynchronously to the

LRCLK and the master clock) as long as they are stable before

the first serial data input bit (i.e., the MSB) is presented to the

AD1857/AD1858.

BCLK

19

18

SCK

WS

SD

LRCLK

SAA2500

20 SDATA

AD1857

AP P LICATIO N ISSUES

Inter face to MP EG Audio D ecoder s

FSCLKIN

HI

HI

MODE

3

6

1

384/256

Figure 15 shows the suggested interface to the Analog Devices

ADSP-21xx family of DSP chips, for which several MPEG

audio decode algorithms are available. T he ADSP-21xx

supports 16 bits of data using a left-justified DSP serial port

style format.

MCLK

256 x F

s

Figure 18. Interface to SAA2500

Figure 19 shows the suggested interface to the Zoran ZR38000*

DSP chip, which can act as an MPEG audio or AC-3 audio

decoder. T he ZR38000 supports 16 bits of data using a left-

justified output format.

19 BCLK

SCLK

RFS

18 LRCLK

NC

NC

SDATA

MODE

20

3

TFS

ADSP-21xx

AD1858

BCLK

SCKB

WSB

19

18

20

3

HI

HI

DT

DR

LRCLK

6

384/256

ZR38000

SDATA

SDB

1

MCLK

NC = NO CONNECT

AD1857

MODE

SCKIN

LO

HI

6

384/256

Figure 15. Interface to ADSP-21xx

1

MCLK

Figure 16 shows the suggested interface to the T exas Instruments

TMS320AV110* MPEG audio decoder IC. The TMS320AV110

supports 18 bits of data using a right-justified output format.

256 x F

s

Figure 19. Interface to ZR38000

Figure 20 shows the suggested interface to the C-Cube

Microsystems CL480* MPEG system decoder IC. T he CL480

supports 16 bits of data using a right-justified output format.

SCLK

LRCLK

BCLK

19

18

20

3

LRCLK

TMS320AV110

PCMDATA

SDATA AD1858

PCMCLK

HI

HI

MODE

BCLK

DA-BCK

DA-LRCK

DA-DATA

19

18

6

384/256

LRCLK

MCLK

1

CL480

20

SDATA

256 x F

s

AD1858

3

6

1

MODE

HI

HI

DA-XCK

Figure 16. Interface to TMS320AV110

384/256

Figure 17 shows the suggested interface to the LSI Logic

L64111* MPEG audio decoder IC. T he L64111 supports 16

bits of data using a left-justified output format.

MCLK

256 x F

s

Figure 20. Interface to CL480

19 BCLK

SCLKO

LRCLKO

SERO

18

20

LRCLK

L64111

SDATA

AD1857

MODE

384/256

MCLK

LO

LO

3

6

1

SYSCLK

384 x F

s

Figure 17. Interface to L64111

*All trademarks are properties of their respective holders.

–12–

REV. 0

ADI [ ADI ]

ADI [ ADI ]