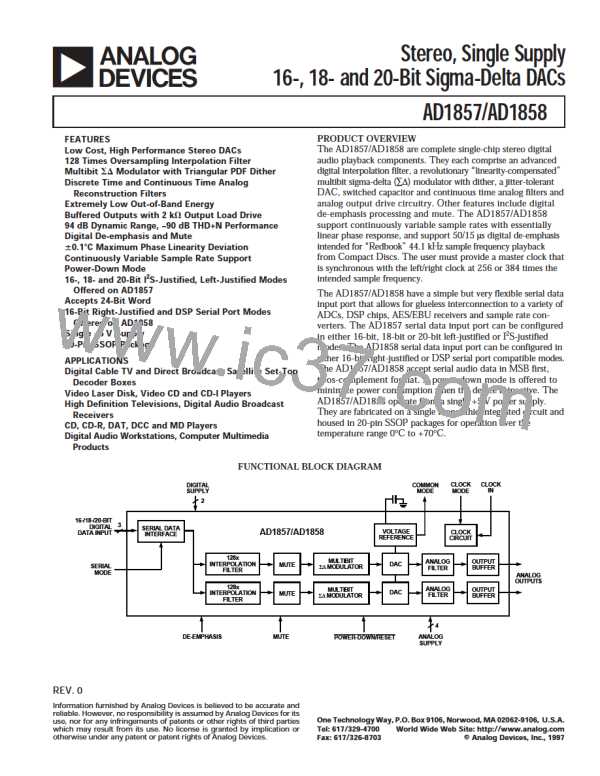

AD1857/AD1858

P IN LIST

D igital Audio Ser ial Input Inter faces

P in Nam e

Num ber

I/O

D escription

SDAT A

20

I

Serial input, MSB first, containing two channels of 16, 18 or 20 bits (AD1857) or

16 bits (AD1858) of twos complement data per channel.

BCLK

19

I

Bit clock input for input data. Need not run continuously; may be gated or used in a

burst fashion.

LRCLK

18

3

I

I

Left/right clock input for input data. Must run continuously.

MODE

Input serial data port mode control. Selects between I2S-justified (HI) and left-justified

(LO) on the AD1857. Selects between DSP serial port style mode (HI) and right-

justified (LO) on the AD1858. The state of the mode pin should be changed only when

the AD1857/AD1858 is held in reset (PD/RST LO). Otherwise, the AD1857/

AD1858 serial port may lose synchronism.

Contr ol and Clock Signals

P in Nam e

Num ber

I/O

D escription

PD/RST

2

I

Power-Down/Reset. T he AD1857/AD1858 are placed in a low power consumption

“sleep” mode when this pin is held LO. T he AD1857/AD1858 are reset on the

rising edge of this signal. Connect HI for normal operation.

DEEMP

5

I

De-emphasis. Digital de-emphasis is enabled when this input signal is HI. T his is

used to impose a 50/15 µs response characteristic on the output audio spectrum at

an assumed 44.1 kHz sample rate.

MUT E

MCLK

15

1

I

I

Mute. Assert H I to mute both stereo analog outputs of the AD1857/AD1858.

Deassert LO for normal operation.

Master Clock Input. Connect to an external clock source at either 256 or 384 times

the intended sample frequency as determined by the 384/256 pin. Must be synchro-

nous with LRCLK, but may have any phase with respect to LRCLK.

384/256

6

I

Selects the master clock mode as either 384 times the intended sample frequency

(H I) or 256 times the intended sample frequency (LO). T he state of this input

should be hardwired to logic LO or logic HI or may be changed while the AD1857/

AD1858 is in power-down/reset. It must not be changed while the AD1857/AD1858

is operational.

Analog Signals

P in Nam e

Num ber

I/O

D escription

FILT

11

O

Voltage Reference Filter Capacitor Connection. Bypass and decouple the voltage

reference with parallel 10 µF and 0.1 µF capacitors to the AGND pin.

CMOUT

10

O

Voltage Reference Common Mode Output. Should be decoupled with 10 µF

capacitor to the AGND pin or plane. T his output is available externally for dc

coupling and level-shifting. CMOUT should not have any signal dependent load,

or used where it will sink or source current.

OUT L

OUT R

8

O

O

Left channel line level analog output.

Right channel line level analog output.

13

P ower Supply Connections and Miscellaneous

P in Nam e

Num ber

I/O

D escription

AVDD

AGND

DVDD

DGND

N/C

7, 14

9, 12

17

I

I

I

I

Analog Power Supply. Connect to analog +5 V supply.

Analog Ground.

Digital Power Supply. Connect to digital +5 V supply.

Digital Ground.

16

4

No Connect. Reserved. Do not connect.

REV. 0

–5–

ADI [ ADI ]

ADI [ ADI ]