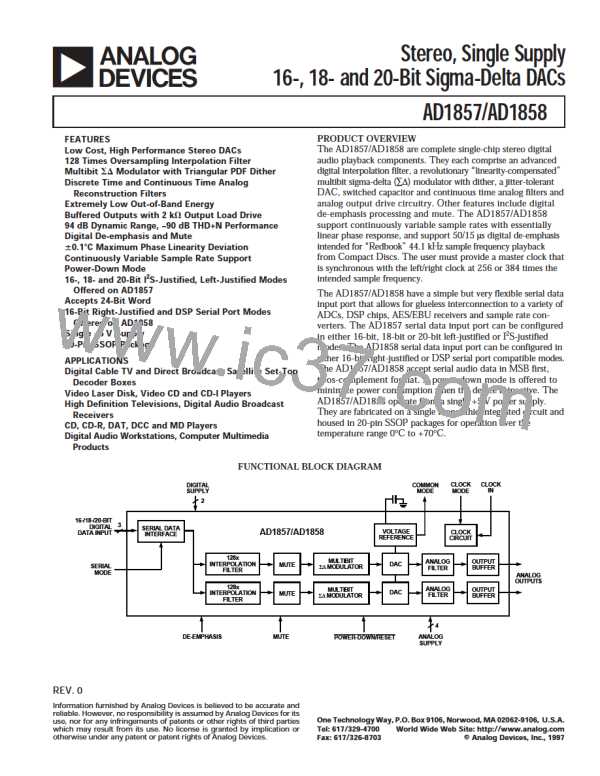

AD1857/AD1858

Tim ing D iagr am s

minimum setup time is tDDS and the minimum serial data hold

time is tDDH

T he serial data port timing is shown in Figures 23 and 24. T he

minimum bit clock HI pulse width is tDBH and the minimum bit

clock LO pulse width is tDBL. T he minimum bit clock period is

.

T he power-down/reset timing is shown in Figure 25. T he

minimum reset LO pulse width is tPDRP (four MCLK periods)

to accomplish a successful AD1857/AD1858 reset operation.

t

DBP. T he left/right clock minimum setup time is tDLS and the

left/right clock minimum hold time is tDLH. T he serial data

tDBH

tDBP

BCLK

tDBL

tDLS

LRCLK

tDDS

SDATA

LEFT-JUSTIFIED

MODE

MSB

tDDH

MSB-1

AD1857

tDDS

SDATA

2

I S-JUSTIFIED

MSB

tDDH

MODE

AD1857

tDDS

tDDS

MSB

SDATA

RIGHT-JUSTIFIED

MODE

LSB

AD1858

tDDH

tDDH

Figure 23. Serial Data Port Tim ing

tDBH

tDBP

BCLK

tDBL

tDLS

tDLH

LRCLK

tDDS

MSB

tDDH

SDATA

LEFT-JUSTIFIED

DSP SERIAL

MSB-1

PORT STYLE MODE

AD1858

Figure 24. Serial Data Port Tim ing–DSP Serial Port Style Mode (AD1858 Only)

MCLK

PD/RST

tPDRP

Figure 25. Power-Down/Reset Tim ing

–14–

REV. 0

ADI [ ADI ]

ADI [ ADI ]