Absolute Maximum Ratings

Operating Junction Temperature, TJ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

Lead Temperature Soldering

Reflow (SMD styles only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60 sec. max above 183°C, 230°C peak

Storage Temperature Range, TS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -65° to 150°C

ESD Susceptibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2kV

VMAX

VMIN

ISOURCE

ISINK

Pin Symbol

VCC1

Pin Name

IC Bias and Low Side Driver

Power Input

16V

-0.3V

N/A

1.5A Peak

200mA

VCC2

IC High Side Driver Power Input

20V

-0.3V

N/A

1.5A Peak

200mA

COMP

VFB, VOUT, VID0-4

Compensation Pin

6V

6V

-0.3V

-0.3V

1mA

1mA

5mA

1mA

Voltage Feedback Input, Output

Voltage Sense Pin, Voltage

ID DAC Inputs

COFF

Off-Time Pin

6V

20V

16V

6V

15V

0V

-0.3V

-0.3V DC

1mA

1.5APeak

200mA DC 200mA DC

1mA

30mA

1.5A Peak

200mA DC

50mA

1.5A Peak

GATE(H)

GATE(L)

PWRGD

OVP

High-Side FET Driver

Low-Side FET Driver

Power-Good Output

Overvoltage Protection

Ground

-0.3V

-0.3V

0V

30mA

1mA

N/A

Gnd

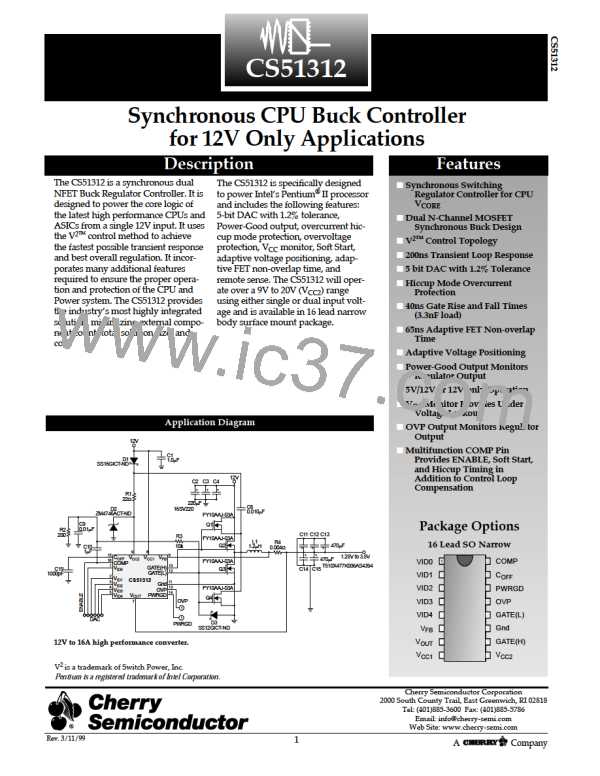

Package Pin Description

PACKAGE PIN #

1,2,3,4,5

PIN SYMBOL

FUNCTION

VIDO – VID4

Voltage ID DAC inputs. These pins are internally pulled up to

5.65V if left open. VID4 selects the DAC range. When VID4 is

high (logic one), the Error Amp reference range is 2.125V to

3.525V with 100mV increments. When VID4 is low (logic zero),

the Error amp reference voltage is 1.325V to 2.075V with 50mV

increments.

6

VFB

Error amp inverting input, PWM comparator non-inverting

input, current limit comparator non-inverting input, PWRGD

and OVP comparator input.

7

8

VOUT

VCC1

Current limit comparator inverting input.

Input power supply pin for the internal circuitry and low side

gate driver. Decouple with filter capacitor to Gnd.

9

VCC2

Input power supply pin for the high side gate driver.

Decouple with filter capacitor to Gnd.

10

11

12

13

GATE(H)

Gnd

GATE(L)

OVP

High side switch FET driver pin .

Ground pin and IC substrate connection.

Low side synchronous FET driver pin.

Overvoltage protection pin. Drives high when overvoltage

condition is detected on VFB.

14

15

16

PWRGD

COFF

Power-Good Output. Open collector output drives low when

VFB is out of regulation.

Off-Time Capacitor Pin. A capacitor from this pin to Gnd sets

the off time for the regulator

Error amp output. PWM comparator inverting input.

A capacitor on this pin provides error amp compensation, and

determines the Soft Start and hiccup timing. Pulling COMP

below 1.1V (typ) turns off both GATE drivers and shuts down

the regulator.

COMP

2

CHERRY [ CHERRY SEMICONDUCTOR CORPORATION ]

CHERRY [ CHERRY SEMICONDUCTOR CORPORATION ]