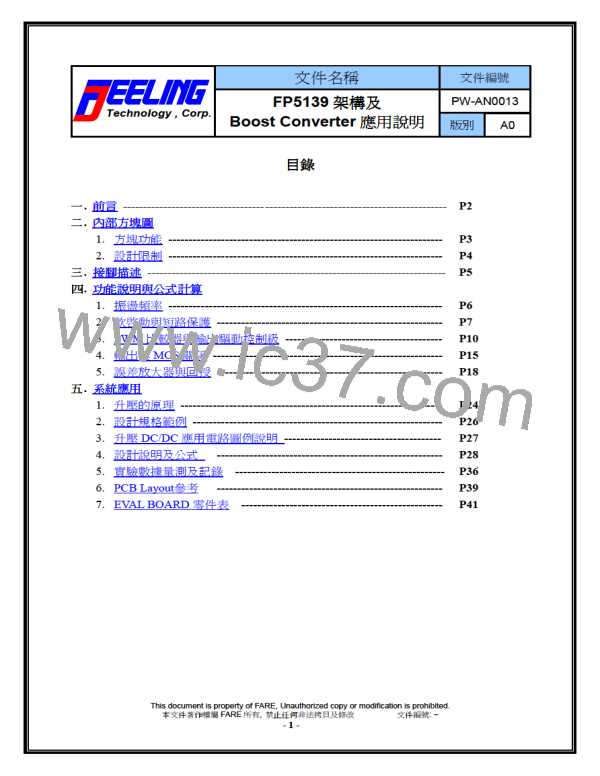

文件編號

文件名稱

PW-AN0013

FP5139 架構及

Boost Converter 應用說明

Technology , Corp.

版別

A0

VOUT −VDS(ON ) +VD

18 − 0.1+ 0.5

∆I =

(1− D

)

D =

(

1− 0.816 0.816 = 0.614(A)

)

L f

10µ 450K

若要維持輸出的漣波低於 50mV,則電容 ESR 要小於 0.08Ω。

輸入電容 C7 則是用於系統電源輸入端做平滑作用,可以利用電荷公式進行計

算;而它的動作在

流的 1/(1-D)倍,若 Iout=200mA 發生在 CCM,則 Iin=1.09A

Iin 及前面 CCM 推算約略可知 IL(DT)-IL(0)= I=614mA,並發生於 DT 時間,

Q 導通時與 Q 關閉時不同,在求輸入平均電流約是輸出電

。

由

∆

若我們希望輸入電壓受負載變動率不得超過 0.5%,即表示 3.3V 的變動範圍在

3.2835V~3.3165V 以內,利用下面公式計算 C7 的最小值:

∆I DT 614

m

1.795

µ

C

7

=

=

= 33.4µ(F)

∆V

0.033

在使用上 C7 必須大於或等於 33.4µF。

升壓應用下由於輸入電流平均值大於輸出,在某種情況下可視為輸入電容的負

載變動率;而其 導通周期的負載特性為電感;又隨輕重負載變動時間產生輸

Q

入電壓差,其輸入電容的 ESR 有時必須被考慮進去。

討論完 L-C 的基本關係式後,就必須考量開關元件的選擇:

Q2

的

I

D 和

Peak 電流卻會到 1.4A(加上ΔI/2),一般設計上我們可以以最大導通周期的

D,但注意當選擇以 peak 時其實平均電流規格也要放大考慮。

DSS 大都有 20V 以上,對升壓 18V 系統而言其發生點 BVDSS 仍然

安全,前面有提過 Q2 的功率損耗計算方法,但我們在這裡要多描述一個很重

要的損耗是交換損失(Switching loss),因為在 450KHz 的工作狀況下 NMOS

ON OFF 時間是處於工作區,如果這段期間過長且功耗也高,實際上會使

NMOS 的溫升過高;另外,由於範例的輸入電壓較低,必須注意NMOS VGS(TH)

這項規格,以AP2304 AP2306 兩種NMOS 而言,很明顯 GS(TH)較高的AP2304

GS(TH)電壓會使 NMOS 在低壓根本無法導

VDSS 規格上很容易看出它在 CCM 下的平均電流是小於 1.09A 但電

感

peak 電流選擇

NMOS 的 V

I

而

的

及

的

及

V

就不能用於該系統中,因為過高的

通。

V

D1的選擇較為單純:一般看ID(M)對VF的關係及注意逆向電壓(Blocking Voltage)

This document is property of FARE, Unauthorized copy or modification is prohibited.

本文件著作權屬 FARE 所有

,

禁止任何非法拷貝及修改

文件編號: ~

- 30 -

ETC [ ETC ]

ETC [ ETC ]