TEA1716T

NXP Semiconductors

Resonant power supply control IC with PFC

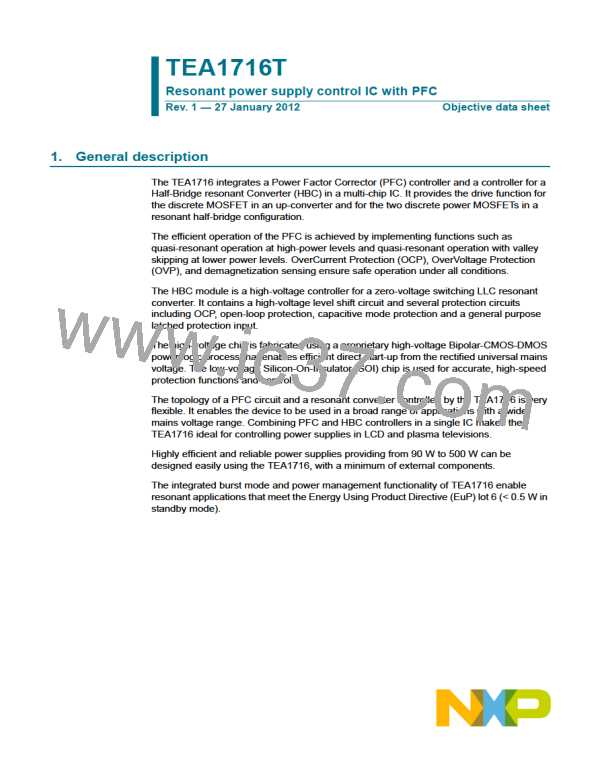

6. Pinning information

6.1 Pinning

1

2

24

23

22

21

20

19

18

17

16

15

14

13

COMPPFC

SNSMAINS

SNSAUXPFC

SNSCURPFC

SNSOUT

SUPIC

SNSBOOST

RCPROT

SSHBC/EN

SNSFB

3

4

5

SNSBURST

CFMIN

6

TEA1716T

7

GATEPFC

PGND

SGND

8

SNSCURHBC

n.c.

9

SUPREG

GATELS

10

11

12

HB

n.c.

SUPHS

SUPHV

GATEHS

aaa-000765

Fig 2. Pin configuration

6.2 Pin description

Table 2. Pin description

Symbol

Pin Description

COMPPFC

SNSMAINS

1

2

frequency compensation for PFC controller; externally connected to filter

sense input for mains voltage; externally connected to resistive divided

mains voltage

SNSAUXPFC

SNSCURPFC

SNSOUT

3

4

5

6

sense input for PFC demagnetization timing; externally connected to

auxiliary winding of PFC

sense input for momentary current and soft start of the PFC controller;

externally connected to current sense resistor and soft start filter

sense input for monitoring the output voltage of the HBC; externally

connected to the auxiliary winding

SUPIC

low-voltage supply for SUPIC input; output of internal HV start-up source;

externally connected to auxiliary winding of HBC or to external DC supply

GATEPFC

PGND

7

8

9

gate driver output for PFC MOSFET

power ground; reference (ground) for HBC low-side and PFC driver

SUPREG

regulated SUPREG IC supply; output from internal regulator; input for

drivers; externally connected to SUPREG buffer capacitor

GATELS

n.c.

10

11

12

gate driver output for low-side MOSFET of HBC

not connected; high-voltage spacer.

SUPHV

high-voltage supply input for internal HV start-up source; externally

connected to boost voltage

GATEHS

SUPHS

13

14

gate driver output for high-side MOSFET of HBC

high-side driver supply input; externally connected to bootstrap capacitor

(CSUPHS

)

TEA1716T

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2012. All rights reserved.

Objective data sheet

Rev. 1 — 27 January 2012

5 of 46

ETC [ ETC ]

ETC [ ETC ]