SigmaTel, Inc.

Data Sheet

STAC9721

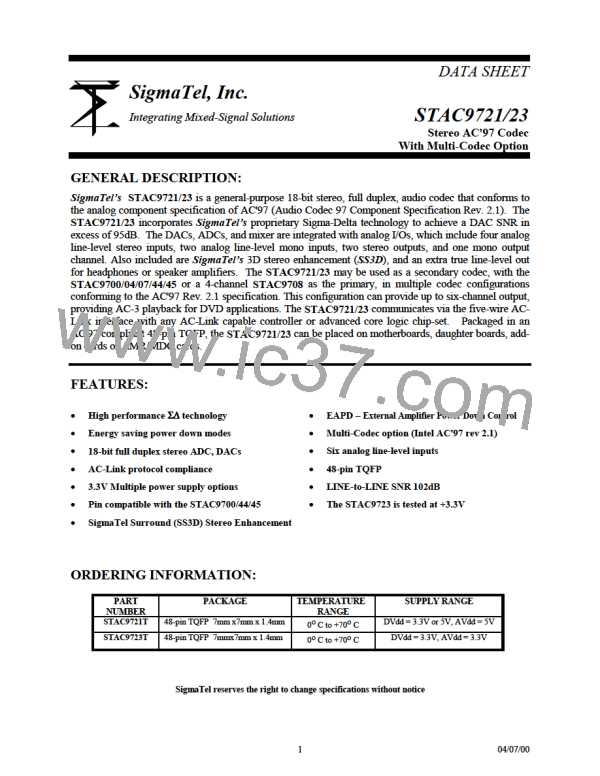

4.4 Programming Registers:

. Programming Registers

Table 7

REG

#

NAME

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

DE-

FAULT

6940h

00h

02h

04h

06h

0Ah

0Ch

0Eh

10h

12h

14h

16h

18h

1Ah

1Ch

20h

22h

26h

28h

6Ch

6Eh

70h

72h

Reset

X

SE4 SE3 SE2 SE1 SE0 ID9 ID8 ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0

Master Volume

LNLVL Volume

Mute

Mute

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

3D

X

ML4 ML3 ML2 ML1 ML0

GL4 GL3 GL2 GL1 GL0

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

0

MR4 MR3 MR2 MR1 MR0

GR4 GR3 GR2 GR1 GR0

MM4 MM3 MM2 MM1 MM0

8000h

8000h

8000h

0000h

8008h

8008h

8808h

8808h

8808h

8808h

8808h

0000h

8000h

0000h

0000h

000Fh

0200h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

8384h

7609h

Master Volume Mono Mute

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

PC_BEEP Volume

Phone Volume

Mic Volume

Mute

Mute

Mute

Mute

Mute

Mute

Mute

Mute

X

X

PV3 PV2 PV1 PV0

X

X

GN4 GN3 GN2 GN1 GN0

GN4 GN3 GN2 GN1 GN0

GR4 GR3 GR2 GR1 GR0

GR4 GR3 GR2 GR1 GR0

GR4 GR3 GR2 GR1 GR0

GR4 GR3 GR2 GR1 GR0

GR4 GR3 GR2 GR1 GR0

20dB

X

Line In Volume

CD Volume

GL4 GL3 GL2 GL1 GL0

GL4 GL3 GL2 GL1 GL0

GL4 GL3 GL2 GL1 GL0

GL4 GL3 GL2 GL1 GL0

GL4 GL3 GL2 GL1 GL0

X

Video Volume

AUX Volume

X

X

PCM Out Volume

Record Select

Record Gain

X

X

X

X

X

X

SL2 SL1 SL0

X

X

X

X

X

X

X

0

X

SR2 SR1 SR0

Mute

X

GL3 GL2 GL1 GL0

X

GR3 GR2 GR1 GR0

General Purpose

3D Control

X

X

X

X

MIX MS LPBK

X

X

X

X

X

X

X

X

X

X

X

X

X

0

X

DP3 DP2

Powerdown Ctrl/Stat EAPD PR6 PR5 PR4 PR3 PR2 PR1 PR0

X

REF ANL DAC ADC

AMAP

Extended Audio ID

Revision Code

ID1 ID0

X

0

X

0

X

0

X

0

X

0

X

X

0

X

0

X

0

X

0

0

0

0

0

Analog Special

X

X

X

X

X

X

X

X

X

X

X

X

X

X

DAC ADC

-6dB -6dB

72h Enable

EN15 EN14 EN13 EN12 EN11 EN10 EN9 EN8 EN7 EN6 EN5 EN4 EN3 EN2 EN1 EN0

Analog Current Adjust

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

Bias1 Bias0

X

74h Multi-Channel Selection

X

MC1 MC0

76h

78h

7Ch

7Eh

78h Enable

Clock Access

Vendor ID1

Vendor ID2

EN15 EN14 EN13 EN12 EN11 EN10 EN9 EN8 EN7 EN6 EN5 EN4 EN3 EN2 EN1 EN0

X

1

0

X

0

1

ALT PWD CLK

X

0

1

X

1

1

X

1

0

X

1

0

X

0

0

X

0

0

X

0

0

X

0

1

X

1

0

OSC

0

X

0

1

CLK

0

0

0

1

1

0

0

Notes:

1. All registers not shown and bits containing an X are reserved.

2. Any reserved bits, marked X, are not writable, and read back as zeros.

3. PC_BEEP default to 0000h, un-muted.

4. If optional bits D13, D5 of register 02h or D5 of register 06h are set to 1, then the corresponding attenuation is set to 46dB and the register

reads will produce 1Fh as a value for this attenuation/gain block.

21

04/07/00

04/07/00

ETC [ ETC ]

ETC [ ETC ]