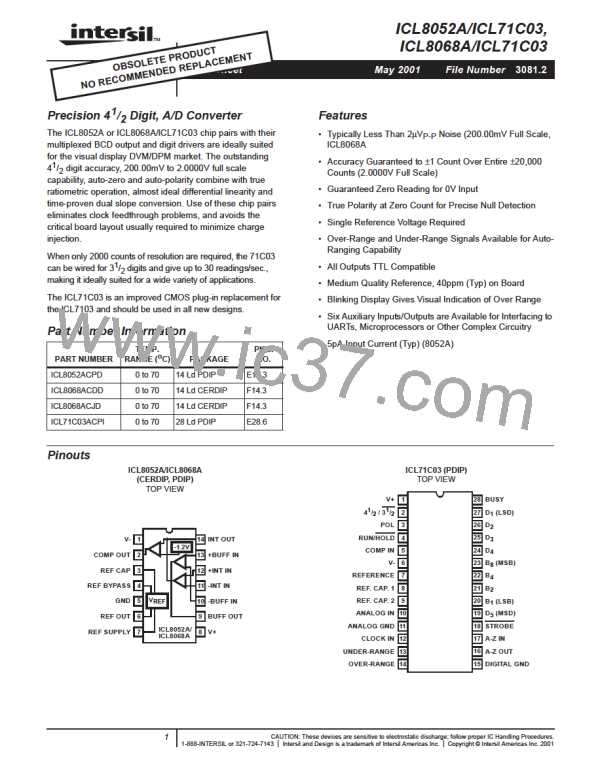

ICL8052A/ICL71C03, ICL8068A/ICL71C03

ICL71C03 with ICL8052A/8068A Integrating A/D Converter Equations

The ICL71C03 does not have an internal crystal or RC

oscillator. It has a clock input only.

Integrator Output Voltage

(t

)(I

)

INT INT

V

= -------------------------------

INT

C

INT

Integration Period

10, 000

V

(Typ) = 9V

INT

t

= -------------------- (4-1/2 Digit)

INT

f

CLOCK

Output Count

1, 000

V

t

= -------------------- (3-1/2 Digit)

IN

INT

f

Count = 10, 000 × -------------- (4-1/2 Digit)

CLOCK

V

REF

Integration Clock Period

= 1/f

V

IN

Count = 1, 000 × -------------- (3-1/2 Digit)

t

V

CLOCK

CLOCK

REF

1

1

NOTE: The 4 / digit mode’s LSD will be output as a zero in the 3 /

2

60/50Hz Rejection Criterion

/t or t /t = Integer

2

digit mode.

t

INT 60Hz INT 50Hz

Output Type:

Optimum Integration Current

= 20µA

4 Nibbles BCD with Polarity and Over-range.

I

INT

Power Supply: 15V, +5V

Full Scale Analog Input Voltage

V++ = +15V

V- = -15V

V+ = +5V

V

(Typ) = 200mV to 2.0V = 2V

REF

INFS

Integrate Resistor

V

≅ 1.75V

REF

REF

If V

(BufferGain) × V

INFS

= ------------------------------------------------------------

not used, float output pin.

R

INT

I

INT

Auto Zero Capacitor Values

Integrate Capacitor

0.01µF < C < 1µF

AZ

(t

)(I

)

INT INT

C

= -------------------------------

Reference Capacitor Value

INT

V

INT

C

= (Buffer Gain) x C

AZ

REF

AUTO ZERO

(COUNTS)

INTEGRATE

DEINTEGRATE

(COUNTS)

(FIXED COUNT)

1

(4 / DIGIT)

2

30,001 - 10,001

3,001 - 1,001

10,000

1,000

1 - 20,001

1 - 2,001

1

(3 / DIGIT)

2

TOTAL CONVERSION TIME (t

)

CONV

(IN CONTINUOUS MODE)

1

t

= 40,002 * t

(4 / DIGIT MODE)

2

CONV

CLOCK

1

t

= 4,002 * t

(3 / DIGIT MODE)

CONV

CLOCK

2

FIGURE 20. INTEGRATOR OUTPUT

20

ETC [ ETC ]

ETC [ ETC ]