Data Sheet

June 1999

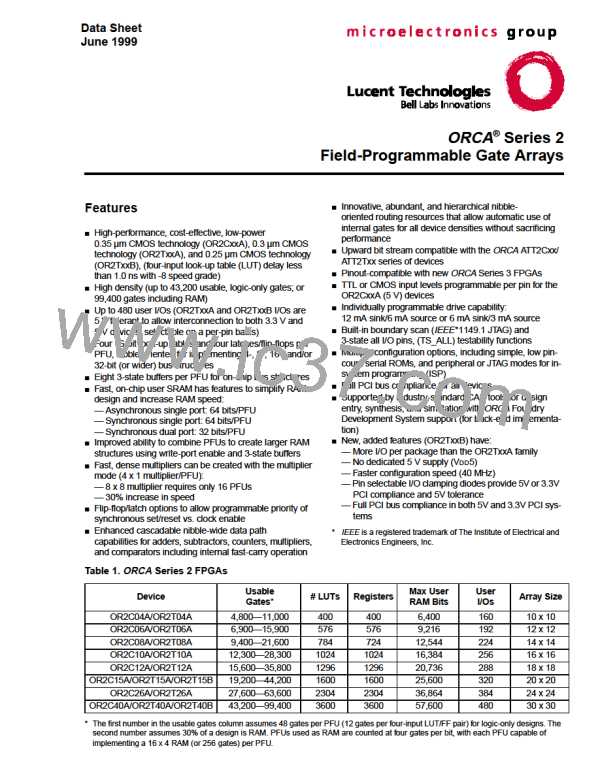

ORCA Series 2 FPGAs

Timing Characteristics (continued)

Table 52A. OR2CxxA/OR2TxxA Slave Serial Configuration Mode Timing Characteristics

OR2CxxA Commercial: VDD = 5.0 V ± 5%, 0 °C ≤ TA ≤ 70 °C; OR2CxxA Industrial: VDD = 5.0 V ± 10%, –40 °C ≤ TA ≤ +85 °C.

OR2TxxA Commercial: VDD = 3.0 V to 3.6 V, 0 °C ≤ TA ≤ 70 °C; OR2TxxA Industrial: VDD = 3.0 V to 3.6 V, –40 °C ≤ TA ≤ +85 °C

Parameter

DIN Setup Time

DIN Hold Time

Symbol

TS

Min

20

0

Max

—

Unit

ns

TH

—

ns

CCLK High Time

CCLK Low Time

CCLK Frequency

CCLK to DOUT

TCH

TCL

FC

50

50

—

—

—

ns

—

ns

10

30

MHz

ns

TD

Note: Serial configuration data is transmitted out on DOUT on the falling edge of CCLK after it is input on DIN.

Table 52B. OR2TxxB Slave Serial Configuration Mode Timing Characteristics

OR2TxxB Commercial: VDD = 3.0 V to 3.6 V, 0 °C ≤ TA ≤ 70 °C; OR2TxxB Industrial: VDD = 3.0 V to 3.6 V, –40 °C ≤ TA ≤ +85 °C.

Parameter

DIN Setup Time

DIN Hold Time

Symbol

TS

Min

15

Max

—

Unit

ns

TH

0

—

ns

CCLK High Time

CCLK Low Time

CCLK Frequency

CCLK to DOUT

TCH

TCL

FC

12.5

12.5

—

—

ns

—

ns

40

10

MHz

ns

TD

—

Note: Serial configuration data is transmitted out on DOUT on the falling edge of CCLK after it is input on DIN

BIT N

DIN

TS

TH

CCLK

DOUT

TCL

TCH

TD

BIT N

5-4535(F)

Figure 70. Slave Serial Configuration Mode Timing Diagram

Lucent Technologies Inc.

165

ETC [ ETC ]

ETC [ ETC ]